## 297-1771-550

**Digital Switching Systems**

## **DMS-Spectrum Peripheral Module**

Hardware Maintenance Reference Manual

DMSSPM15 Standard 05.02 April 2001

# Digital Switching Systems DMS-Spectrum Peripheral Module

Hardware Maintenance Reference Manual

Publication number: 297-1771-550 Product release: DMSSPM15 Document release: Standard 05.02 Date: April 2001

Copyright © 1999-2001 Nortel Networks, All Rights Reserved

Published in the United States of America

**NORTEL NETWORKS CONFIDENTIAL:** The information contained herein is the property of Nortel Networks and is strictly confidential. Except as expressly authorized in writing by Nortel Networks, the holder shall keep all information contained herein confidential, shall disclose the information only to its employees with a need to know, and shall protect the information, in whole or in part, from disclosure and dissemination to third parties with the same degree of care it uses to protect its own confidential information, but with no less than reasonable care. Except as expressly authorized in writing by Nortel Networks, the holder is granted no rights to use the information contained herein.

Nortel Networks, the Nortel Networks logo, the Globemark, How the World Shares Ideas, and Unified Networks are trademarks of Nortel Networks.

## **Publication history**

## April 2001

Standard 05.02 SP15 (CSP15). Added/changed the following for the release:

- Added the NTLX91BA SPM-DMS frame assembly

- Added notes relate to the NTLX63AA CEM not being compatible with SP15 or later

- SR NR10722 removed the following alarms from Chapter 2, "Visual alarm indicators":

- CSS

- CV

- CVFE

- ES

- ESFE

- LBC

- OPT

- OPR

- SEFS

- SES

- SESFE

- UAS

- UASFE

## February 2001

Standard 05.01 SP15 (CSP15). Added/changed the following for the release:

| • Added the NTLX82BA CEM per features 59018984 and 59019804.                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Made editorial changes to Chapter 1, "Introduction", and Chapter 2, "Visual alarm indicators."                                                              |

| • Made the following changes to Chapter 3, "Hardware descriptions:"                                                                                           |

| <ul> <li>Modified the resource modules listed in the "NTLX51AA dual-shelf<br/>assembly" and "NTLX51BA dual-shelf assembly"</li> </ul>                         |

| <ul> <li>Modified the suggested locations listed in the "NTLX65BA DSP RM",<br/>"NTLX66BA VSP RM", "NTLX72AA DLC RM", and<br/>"NTLX85/86AA VSP RM."</li> </ul> |

| <ul> <li>Made editorial updates to reflect the suggested use of the NTLX51BA<br/>dual-shelf assembly over the NTLX51AA.</li> </ul>                            |

| Standard 04.03 SP14 (CSP13/14). Updated the NTLX51AA and NTLX51BA dual-shelf assemblies per SR 10366713.                                                      |

| Standard 04.02 SP14 (CSP13/14). Released due to late SME comments.                                                                                            |

| Standard 04.01 SP14 (CSP13/14). Updated the DSP RM provisioning guidelines per SME's email dated July 27, 2000.                                               |

| Standard 03.05 SPM12 (CSP12). Updated the NTLX85/86AA VSP RM section per SR 10343869.                                                                         |

| Standard 03.04 SPM12 (CSP12).                                                                                                                                 |

| • Made revisions to the ATM RM, NTLX73AA                                                                                                                      |

| • Made revisions to the DLC RM, NTLX72AA                                                                                                                      |

| • Made revisions to the OC3 RM, NTLX71BA                                                                                                                      |

|                                                                                                                                                               |

• Added the NTLX51BA dual-shelf assembly

#### February 2000

Standard 03.03 SPM12 (CSP12). Added optical interface specifications to the OC3 RM section of the document per SR CH90186.

#### January 2000

Standard 03.02 SPM12 (CSP12).

- Made revisions to the CEM RM, NTLX82AA.

- Included the ATM RM, NTLX73AA.

- Added the DLC RM, NTLX72AA.

#### December 1999

Preliminary 03.01 SPM12 (CSP12).

#### August 1999

Upissued to Standard 02.03 SPM11 (CSP11) to add NTLX82AA common equipment module (CEM) based on SR NV90426.

#### July 1999

Standard 02.02 SPM11 (CSP11).

The information regarding the NTLX73AA asynchronous transfer mode (ATM) resource module (RM) has been moved to the "ATM General Description," 297-1771-150.

Made editorial changes.

#### June 1999

Preliminary 02.01 SPM11 (CSP11).

- Feature AF7378 added hardware procedure for ATM RM, NTLX73AA.

- Made editorial changes

#### February 1999

Standard 01.05 SPM01 (CSP09). Changed the product name to "DMS-Spectrum Peripheral Module (SPM)." Added information about DSP provisioning to the "NTLX65AA DSP RM."

#### October 1998

Standard 01.04 is the initial release for SPM01 (CSP09).

## Contents

| Ab | out this document<br>When to use this document ix          | ix  |

|----|------------------------------------------------------------|-----|

|    | Audience and applicability ix                              |     |

|    | How to check the version and issue of this document ix     |     |

|    | Related NTPs ix                                            |     |

| 1  | Introduction                                               | 1-1 |

| 2  | Visual alarm indicators                                    | 2-1 |

|    | MAP terminal 2-1                                           |     |

|    | SPM alarm classifications 2-2                              |     |

|    | Significance of alarm indicators 2-4                       |     |

|    | SPM alarms 2-6                                             |     |

| 3  | Hardware descriptions                                      | 3-1 |

|    | NT9X40DA paddleboard 3-2                                   |     |

|    | NTLX50AA SPM-DMS frame assembly 3-10                       |     |

|    | NTLX51AA dual-shelf assembly 3-20                          |     |

|    | NTLX51BA dual-shelf assembly 3-28                          |     |

|    | NTLX55AA cooling unit and grill assemblies 3-37            |     |

|    | NTLX57AA PCIU 3-41                                         |     |

|    | NTLX60AA filler module 3-51                                |     |

|    | NTLX61AA SIM 3-53                                          |     |

|    | NTLX63AA CEM 3-58                                          |     |

|    | NTLX65BA DSP RM 3-70                                       |     |

|    | NTLX66BA VSP RM 3-81<br>NTLX71BA OC3 interface module 3-90 |     |

|    | NTLX7TBA OCS Interface module 3-90<br>NTLX72AA DLC 3-103   |     |

|    | NTLX82AA CEM 3-110                                         |     |

|    | NTLX82BA CEM 3-128                                         |     |

|    | NTLX85/86AA VSP RM 3-146                                   |     |

|    | NTLX91BA SPM-DMS frame assembly 3-155                      |     |

List of terms

A-1

## About this document

## When to use this document

Use this document when you need maintenance information about the hardware components of the DMS-Spectrum Peripheral Module (SPM).

## Audience and applicability

This document provides information for operating company personnel responsible for SPM installation, provisioning, and maintenance. This manual also provides information for others who are interested in a general description of the SPM features and hardware.

## How to check the version and issue of this document

The version and issue of the document are indicated by numbers, for example, 01.01.

The first two digits indicate the version. The version number increases each time the document is updated to support a new software release. For example, the first release of a document is 01.01. In the *next* software release cycle, the first release of the same document is 02.01.

The second two digits indicate the issue. The issue number increases each time the document is revised but released again in the *same* software release cycle. For example, the second release of a document in the same software release cycle is 01.02.

This document is written for all DMS-100 Family offices. More than one version of this document may exist. To determine whether you have the latest version of this document and how the documentation for your product is organized, check the release information in *Product Documentation Directory*, 297-8991-001.

You should be familiar with the DMS system and DMS peripheral modules (PM) before you attempt to use the information in this manual.

## **Related NTPs**

Refer to the following documents for more information about SPM:

- DMS-Spectrum Peripheral Module Service Implementation Guide, 297-1771-301.

- DMS-Spectrum Peripheral Module Feature Description Reference Manual, 297-1771-330.

- DMS-Spectrum Peripheral Module Commands Reference Manual, 297-1771-819.

- SPM information is also included in the following NTPs:

- Trouble Locating and Clearing Procedures

- Alarm Clearing Procedures

- Recovery Procedures

- Routine Procedures

- Card Replacement Procedures

- Operational Measurements

- Data Schema

- Logs

## **1** Introduction

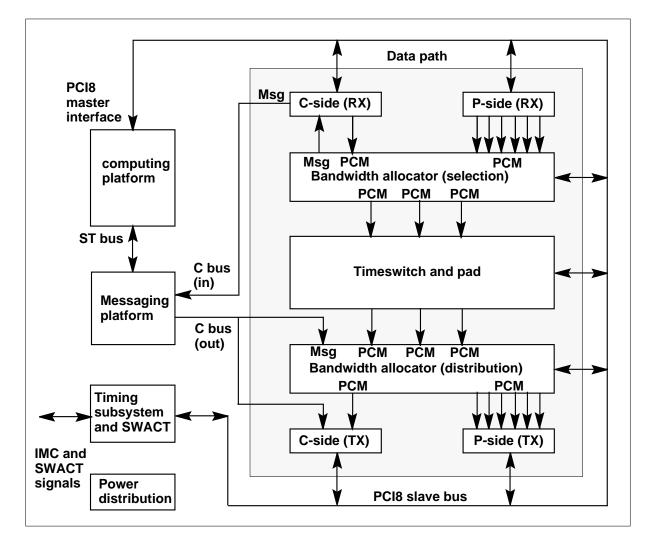

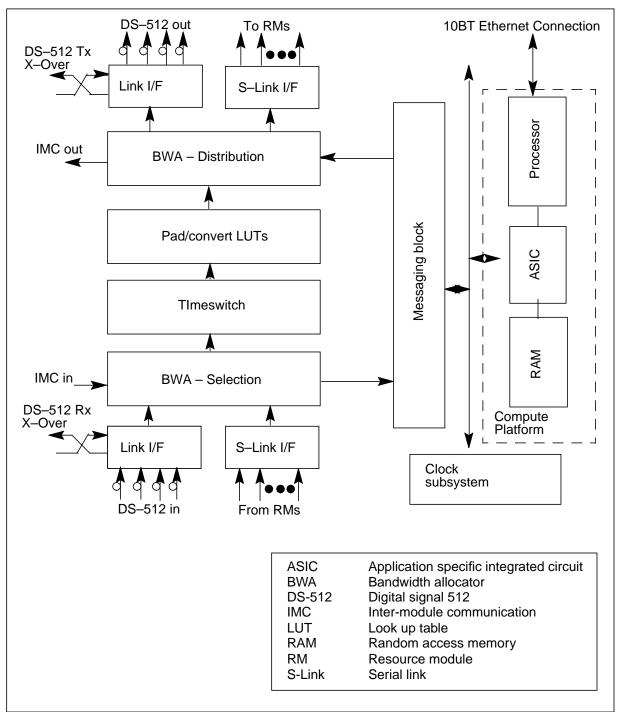

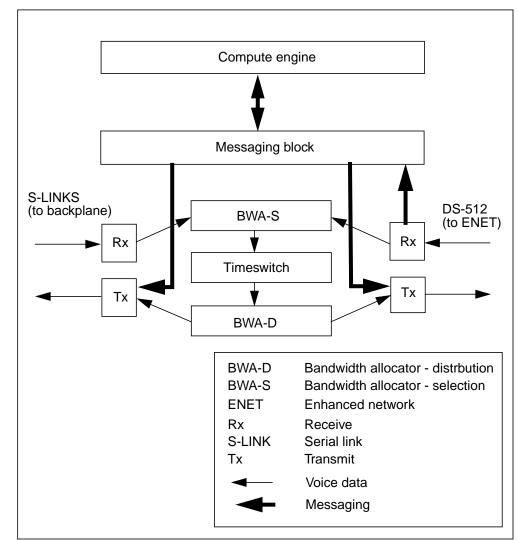

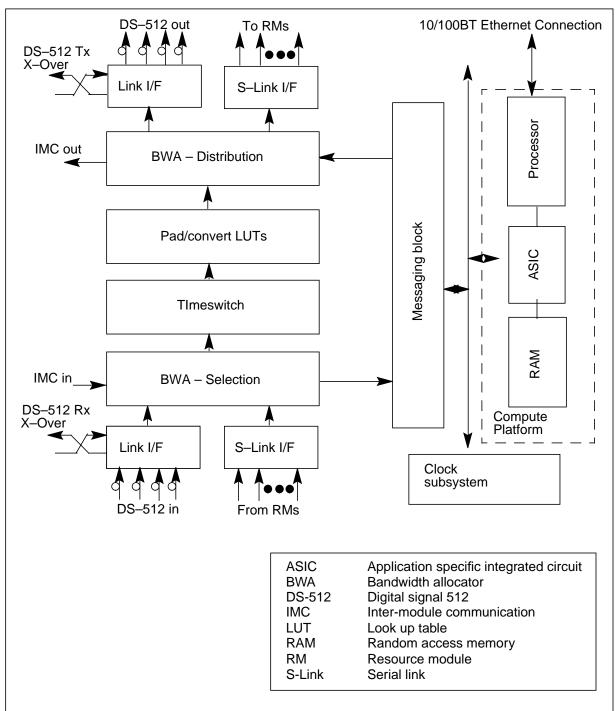

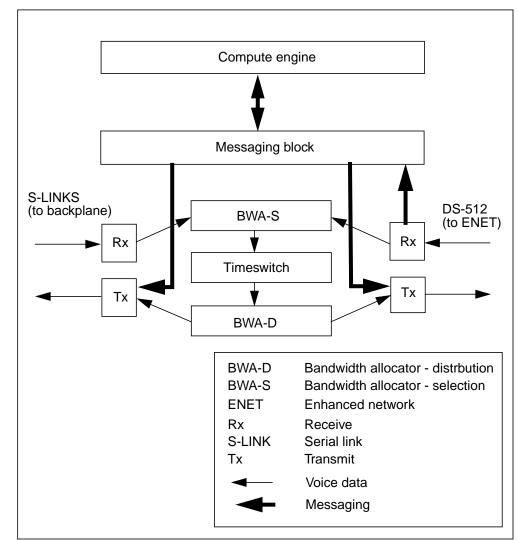

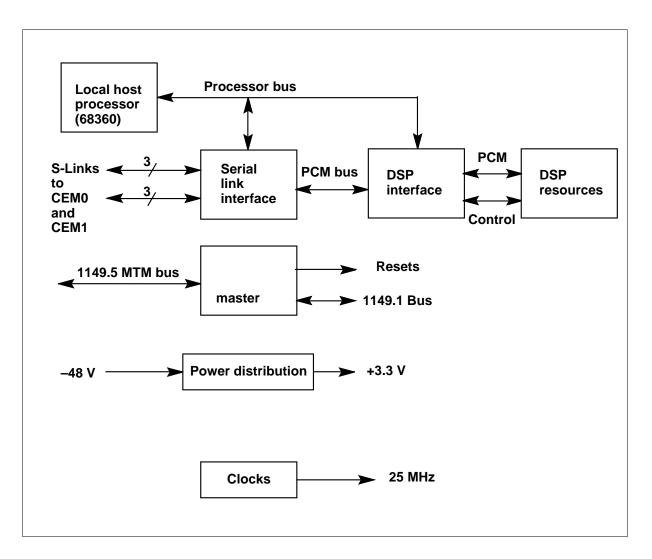

The DMS-Spectrum Peripheral Module (SPM) is functionally equivalent to a digital trunk controller for interswitch trunks. It provides common channel signaling #7 and per-trunk signaling speech and data trunks on TR-782 compliant Optical Carrier 3 (OC3) carriers. Internally, all trunks are treated as DS-0s or as sets of DS-0s.

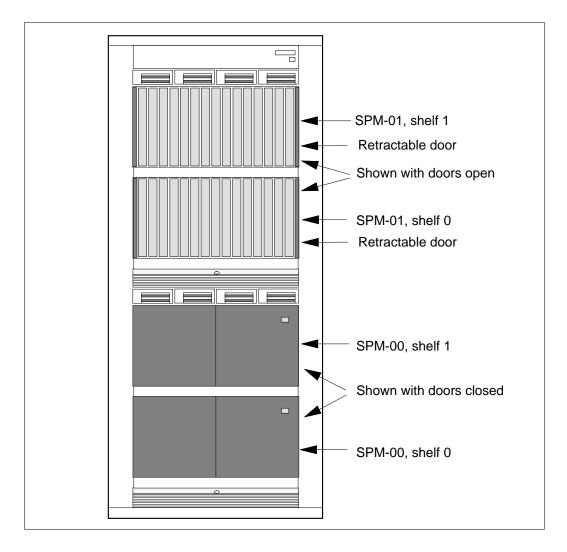

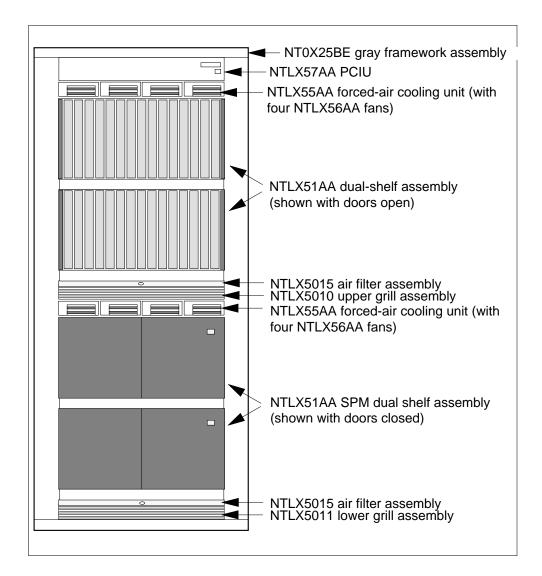

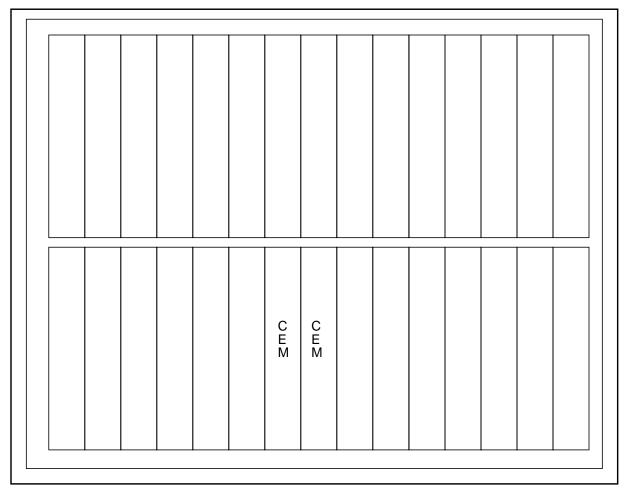

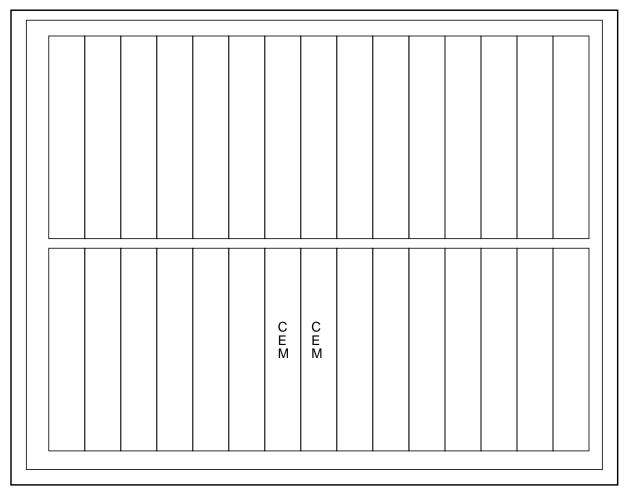

As shown in the following figure, the NTLX91BA frame assembly contains two NTLX51AA or NTLX51BA dual-shelf assemblies (two complete SPMs) and the necessary support equipment. Each dual-shelf assembly provides 30 slots to accommodate

- two NTLX61AA shelf interface modules (SIM)—one SIM needs to be one each shelf on the dual-shelf assembly

- two NTLX63AA, NTLX82AA, or NTLX82BA common equipment modules (CEMs) for each dual-shelf assembly

*Note:* The NTLX63AA CEM is not compatible with SP15 or later.

- two NTLX71AA or NTLX71BA OC3 interface modules for each dual-shelf assembly

- two NTLX72AA data link controller (DLC) RMs for each dual-shelf assembly

- 0 to 24 NTLX65AA or NTLX65BA digital signal processor (DSP) resource modules (RMs) or NTLX66AA, NTLX66BA, NTLX85AA, or NTLX86AA voice signal processor (VSP) RMs for each dual-shelf assembly

*Note:* Support exists for any combination of up to 24 DSP and VSP RMs. Typically, the number of necessary DSP and VSP RMs will be less than this.

#### ATTENTION

Not all modules apply to all markets.

The NTLX55AA cooling unit provides forced-air cooling to the SPM equipment by four NTLX56AA fan assemblies.

The NTLX57 PCIU serves as a central gathering point for all power and alarm cabling used within the NTLX91BA frame assembly.

The NT9X40DA paddleboard provides the SPM interface to the DMS switch and the enhanced network (ENET). The paddleboard supports four SPM DS-512 connections to the ENET.

## 2 Visual alarm indicators

The DMS-Spectrum Peripheral Module (SPM) frames and modules have visual alarm indicators, which are connected to the DMS aisle alarm indicators.

## **MAP** terminal

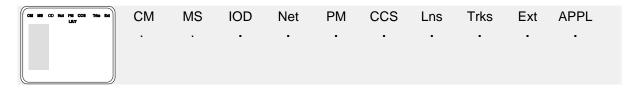

The MAP terminal displays the following alarm.

If an alarm is reportable and a higher level alarm does not mask it, the alarm indicator appears under the peripheral module (PM) category of the alarm banner on the MAP terminal.

Alarm indicators consist of two lines that include the following elements:

- *xxyyy*

- ZZZ

*xx*: represents the number of the SPM unit with at least one alarm of the same severity

yyy represents the type of device, which is always SPM for SPM units

zzz represents one of the following severity codes

- $*C^*$  critical alarm

- M major alarm

- <blank> minor alarm

- — no alarm

A higher level alarm masks all levels below it. For example, a critical (\*C\*) alarm masks both major (M) and minor () alarms. If lower level alarms are present, they are reported in a log.

When there are no alarms, a dot (•) appears in the device field (xxyyy).

#### List command

You can display a list of the alarms at all levels using the LISTALM command.

#### Logs

Each reportable alarm generates a log containing information about the alarm.

## **SPM** alarm classifications

There are three different causes of SPM alarms, and these alarms are reported by various devices. These devices can be part of the SPM or part of the DMS alarm reporting system.

The following can cause SPM alarms:

- device failures

- network events

- threshold crossings

The following can report SPM alarms:

- an SPM network node

- individual SPM modules

- the DMS computing module (CM), which reports alarms for

- input/output devices (IOD)

- common channel signaling (CCS)

- trunks (TRKS)

- carriers (CARR)

#### **Device failures**

Physical devices generate alarms when a detectable failure occurs. SYSBNA is an example of this type of alarm.

#### **Network events**

Various sources generate network-event alarms when monitored events occur on the network. AIS and LOS are examples of this type of alarm.

#### **Threshold crossings**

Alarms generate when monitored parameters or metered parameters exceed their datafilled settings. SPM devices or network events, or both, can cause these alarms. COTLOW and VCXO70 are examples of these types of alarms.

### SPM network node

An SPM node consists of all the modules on shelves 0 and 1, which connect to the OC-3 network through the OC-3 modules in slot 9 and slot 10 on shelf 0.

#### **SPM** modules

The following SPM modules can generate alarms:

- common equipment module (CEM)

- OC-3 interface module (OC-3)

- DLC interface module (DLC)

- digital signal processor (DSP)

- voice signal processor (VSP)

*Note:* The VSP does not apply to all markets.

### DMS computing module

SONET carriers can generate alarms at the following DMS computing module (CM) alarm reporting levels:

- trunks (Trks)

- input/output devices (IOD)

- common channel signaling (CSS)

#### Threshold-crossing alarms

The SPM CEM and the DMS CM can generate threshold-crossing alarms. Threshold-crossing alarms are one of the following types:

- steady-state faults

- performance parameters

- metered-performance parameters

You can enter high-threshold and low-threshold values for the various alarms in DMS data schema tables. Refer to the *Data Schema Reference Manual* or the data schema section of the *Translation Guide*, as appropriate. Alarms generate when the high-value threshold is crossed and they clear when the low-value threshold is crossed. See the alarm descriptions for the appropriate data schema table references.

#### Steady state faults

Steady state faults, or soaked defects, occur when a performance parameter crosses an upper threshold and remains above the lower threshold value for an extended period. AIS and RFI are examples of steady-state fault alarms.

#### **Performance parameters**

Performance parameters are counts of intermittent defects. Alarms generate when counts exceed threshold values. Performance parameters are collected over 15-minute periods and 1-day periods. Performance parameter counts are reset when collection periods end. CV and ES are examples of performance parameter alarms.

#### Metered performance parameters

Metered performance parameters are physical measurements. Alarms generate when a measured value exceeds its benchmark setting by the datafilled percentage. Benchmark settings can be reset. LBR and OPT are examples of metered performance parameter alarms.

## Significance of alarm indicators

Alarm indicators are LEDs that appear at the top of each frame and at the top of the faceplate on each SPM module. All modules have a red and a green module-status indicator. Modules with external connections on the faceplate also have an additional amber signal-status indicator, which indicates the status of the external connections.

See the following tables for information about the significance of individual alarm indicators and alarm-indicator combinations.

| Module-condition LED combinations |     |                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Green                             | Red | Indication and action                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Off                               | Off | Green LEDs are in sleep mode (module can also be not<br>powered or not seated). When all LEDs are off, there<br>are no critical faults and an indicator test is not<br>underway. Use an indicator test to check LED function.                                                                                                                                         |  |  |  |  |

| On                                | On  | A power on self test (POST) or an LED indicator test is<br>underway. During a POST, the LEDs are controlled by<br>the initial boot loader (IBL) software. If both LEDs<br>remain on for an extended period after a POST, the<br>module is defective. For detailed instructions for<br>replacement, see the appropriate <i>Card Replacement</i><br><i>Procedures</i> . |  |  |  |  |

| On                                | Off | Normal operation—there are no critical faults and no action is required. Do not remove a module displaying this alarm-indicator combination.                                                                                                                                                                                                                          |  |  |  |  |

| Off                               | On  | Critical fault—replace the module.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                   | •   | ED life, program the green LEDs so it can enter the sleep<br>ode timing is controlled by the entry in field LEDTIMER in                                                                                                                                                                                                                                               |  |  |  |  |

#### Table 1

Table 2

| External signal-status LEDs                           |                                                                                                         |  |  |  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| Amber                                                 | Indication                                                                                              |  |  |  |

| Off                                                   | Normal operation—all external signal inputs to the module faceplate are valid.                          |  |  |  |

| On                                                    | At least one external signal source<br>entering the module faceplate is not<br>carrying a valid signal. |  |  |  |

| <i>Note:</i> Sleep mode does not apply to amber LEDs. |                                                                                                         |  |  |  |

data schema table MNNODE. Sleep mode does not apply to red LEDs.

*Note:* Alarm indicators do not indicate maintenance states (such as manual busy, in service, or in service trouble) or activity states (active or inactive).

## SPM alarms

The following table lists the alarms for the SPM and indicates the resource or control parameter generating the alarm.

### Table 3 (Sheet 1 of 2)

| Source device or parameter |             |           |          |     |     |     |             |               |              |

|----------------------------|-------------|-----------|----------|-----|-----|-----|-------------|---------------|--------------|

| AlarmName                  | SPM<br>Node | CEM       | OC-3     | DSP | VSP | DLC | DMS<br>TRKS | CARR<br>METER | CARR<br>PERF |

| Alarms appeal              | ring unde   | er the PM | l banner |     |     |     |             |               |              |

| CLKOOS                     |             | Х         |          |     |     |     |             |               |              |

| COTLOW                     | Х           |           |          |     |     |     |             |               |              |

| DTMFLOW                    | Х           |           |          |     |     |     |             |               |              |

| ECANLOW                    | Х           |           |          |     |     |     |             |               |              |

| HLDOVR                     |             | Х         |          |     |     |     |             |               |              |

| HLDOVR24                   |             | Х         |          |     |     |     |             |               |              |

| MANB                       | Х           | Х         | Х        | Х   | Х   | Х   |             |               |              |

| MANBNA                     | Х           | Х         | Х        | Х   | Х   | Х   |             |               |              |

| MFLOW                      | Х           |           |          |     |     |     |             |               |              |

| ISTB                       | Х           | Х         |          |     |     | Х   |             |               |              |

| NOSPARE                    |             |           | Х        | Х   | Х   | Х   |             |               |              |

| PROTFAIL                   |             |           | Х        | Х   | Х   | Х   |             |               |              |

| SYSB                       | Х           | Х         | Х        | Х   | Х   | Х   |             |               |              |

| SYSBNA                     | Х           | Х         | Х        | Х   | Х   | Х   |             |               |              |

| TONESLOW                   | Х           |           |          |     |     |     |             |               |              |

| VCXO70                     |             | Х         |          |     |     |     |             |               |              |

| VCXO90                     |             | Х         |          |     |     |     |             |               |              |

| Alarms appeal              | ring unde   | er the TR | KS bann  | er  |     |     |             |               |              |

| AIS                        |             |           |          |     |     |     | Х           |               |              |

| BERSD                      |             |           |          |     |     |     | Х           |               |              |

| BERSF                      |             |           |          |     |     |     | Х           |               |              |

#### Table 3 (Sheet 2 of 2)

| Source device or parameter |             |     |      |     |     |     |             |               |              |

|----------------------------|-------------|-----|------|-----|-----|-----|-------------|---------------|--------------|

| AlarmName                  | SPM<br>Node | СЕМ | OC-3 | DSP | VSP | DLC | DMS<br>TRKS | CARR<br>METER | CARR<br>PERF |

| LOF                        |             |     |      |     |     |     | Х           |               |              |

| LOP                        |             |     |      |     |     |     | Х           |               |              |

| LOS                        |             |     |      |     |     |     | Х           |               |              |

| RAI                        |             |     |      |     |     |     | Х           |               |              |

| RFI                        |             |     |      |     |     |     | Х           |               |              |

| SIMPLEX                    |             |     |      |     |     |     | Х           |               |              |

## **3 Hardware descriptions**

This chapter describes the hardware components of the DMS-Spectrum Peripheral Module (SPM). The component descriptions follow a top-to-bottom order. The chapter describes the following components:

- NT9X40DA paddleboard

- NTLX50AA SPM-DMS frame assembly

*Note:* The NTLX50AA SPM-DMS frame assembly is not compatible with releases after SP11.

- NTLX51AA dual-shelf assembly

- NTLX51BA dual-shelf assembly

- NTLX55AA cooling unit and grill assemblies

- NTLX57AA PCIU

- NTLX60AA filler module

- NTLX61AA shelf interface modules (SIM)

- NTLX63AA common equipment modules (CEM)

Note: The NTLX63AA CEM is not compatible with SP15 or later.

- NTLX65BA DSP RM

- NTLX66BA VSP RM

- NTLX71BA OC-3 interface module

- NTLX72AA DLC RM

- NTLX82AA common equipment modules (CEM)

- NTLX82BA common equipment modules (CEM)

- NTLX85AA and NTLX86AA VSP RM

- NTLX91BA SPM-DMS frame assembly

*Note:* Not all modules apply to all markets.

## NT9X40DA paddleboard

## Description

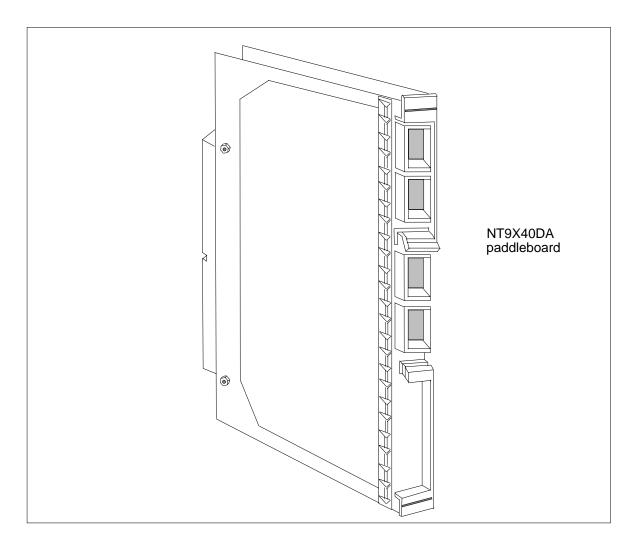

The DMS-Spectrum Peripheral Module (SPM) uses the NT9X40DA paddleboard to interface with the DMS switch through the enhanced network (ENET) crosspoint (XPT) card.

The NT9X40DA ENET quad DS-512S fiber link interface is one of several SuperNode or SuperNode SE ENET paddleboards. The NT9X40DA paddleboard uses four hard-clad silica (HCS) fibers operating at 650 nm wavelength to provide 2048 channels to the ENET XPT cards.

The NT9X40DA is the only network interface paddleboard that currently supports hard-clad silica fiber and it cannot be substituted for any of the other fiber link interface paddleboards such as the NT9X40BA or the NT9X40BB.

## Location

As shown in the following figure, the NT9X40DA ENET paddleboard resides in the ENET shelf and connects to the common equipment module (CEM) in the SPM using HCS fiber-optic cable.

## **Dependencies**

The DMS message switch (MS) must have a minimum of the following items to provide the ENET functionality required by the SPM connected to the NT9X40DA paddleboard:

- NT9X13DC, MS CPU Processor CP (4 Mbytes)

- NT9X17DA, MS 64-Port CP

- NT9X20BB, ENET/MS Fiber Interface PB

- NT9X25AA, MS Port Expander PB

- NT9X25BA, MS Port Expander/Terminator PB

- NT9X49CB, MS P-Bus Terminator CP (Tracer Card)

*Note 1:* To interface with the ENET, the MS requires 10 Mbytes of memory.

*Note 2:* The NT9X25AA and NT9X25BA are required only if a chain of NT9X17DAs are installed.

*Note 3:* A 128-port NT9X17CA card must be paired with an 9X20BC card.

## Features

The NT9X40DA paddleboard provides the following features:

- lower cost electro-optic modules and connectors

- easy cable termination

- smaller bend radius of HCS fiber

- duplex keyed connector (no reversing RX and TX)

- simpler connect and disconnect action

- visible wavelength

- embedded maintenance channel

- alarm codes replaced by status bits

- embedded cycle redundancy checking (CRC)

- enhanced reset capability

- more robust and more integrated clock recovery

## **Functions**

The NT9X40DA paddleboard provides the following:

- four DS-512S fibers

- 2048 channels

- 16-bit CRC

- ENET shelf processor access to the processor bus (PBus)

## **Functional blocks**

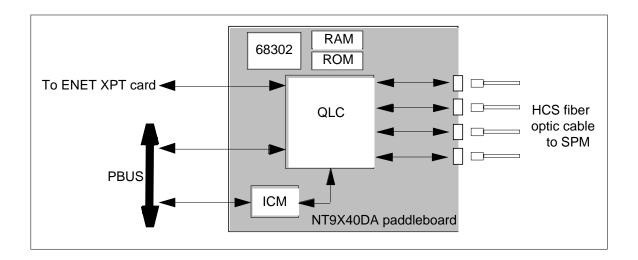

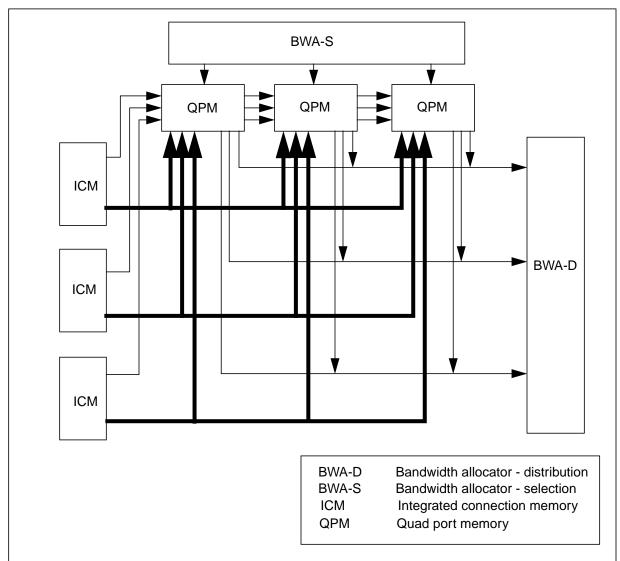

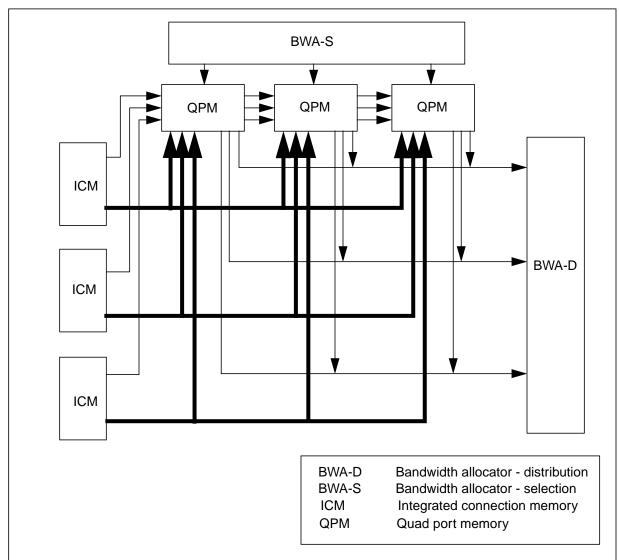

NT9X40DA paddleboard consists of the following functional blocks:

- fiber interface and quad link chip (QLC)

- pad connection memory using integrated connection memory (ICM)

- 68302 integrated processor

- PBus interface

## Fiber interface and the quad link chip (QLC)

The fiber interface and the QLC provide

- four DS-512S fiber transmit/receive pairs

- multiplexed frame channel

- out-of-band maintenance and messaging

- facility data link (FDL) channel

- local processor interface

- maintenance and messaging internal registers

- full frame elastic store for each DS-512S receive link

- pseudo-random bit sequence (PRBS) data insertion and extraction

- CRC-16 error correction

- 2048, 10-bit ENET channels

#### Pad connection memory

The pad connection memory uses an ICM to provide  $\pm 7 \text{ dB DS-0}$  pads that are adjustable in 1 dB steps. The ICM is used as the gain or loss pad connection memory.

#### Integrated processor

The 68302 integrated processor block contains a central processing unit (CPU), a flash read-only memory for CPU firmware, and static RAM for incoming and outgoing message storage. The integrated processor performs the following major functions as well as other minor functions:

- inserts the FDL message information protocol

- responds to QLC interrupts

- stores messages in transit between the ENET shelf processor and the CEM

#### **PBus interface**

The PBus provides the bus connection to the ENET shelf processor and shelf processor access to the identification programmable ROM.

## Signaling

The following table shows power pin numbers.

| Pin number                                                                           | Signal | Function | Description             |

|--------------------------------------------------------------------------------------|--------|----------|-------------------------|

| 26A, 29A, 32A, 37A, 38A, 43A,<br>48A, 53, 59A, 59B, 59C, 65A,<br>65B, 65C, 65D       | GND    | power    | Logic ground            |

| 27A, 28A, 30A, 31A, 39A, 40A,<br>41A, 42A, 44A, 45A, 46A, 47A,<br>49A, 50A, 51A, 52A | +5.0 V | power    | +5.0 volts power supply |

| 33A, 34A, 35A, 36A                                                                   | -5.2 V | power    | -5.2 volts power supply |

| Pin number | Signal           | Function | Description                                                                                   |

|------------|------------------|----------|-----------------------------------------------------------------------------------------------|

| 46D, 47D   | CK21P+, CK21P-   | input    | 49.152 MHz DS-512S clock, provided by the 9X35 crosspoint card.                               |

| 48D, 49D   | NFP21P+, NFP21P- | input    | System frame pulse (active low) 8<br>kHz provided by the 9X35<br>crosspoint card frame pulse. |

| 50D        | CK61             | input    | 16.384 MHz system clock                                                                       |

| 51D        | NFP61            | input    | System frame pulse (active low) 8<br>kHz, frame pulse width one CK61<br>clock cycle           |

| 52D        | NTFP61           | input    | System transmit frame pulse (active<br>low) 8 kHz, frame pulse width on<br>CK61 clock cycle   |

The following table shows the clock pin numbers.

The following table shows the processor interface signal pin numbers.

#### (Sheet 1 of 2)

| Pin<br>number                                   | Signal                                                                  | Function  | Description                                                                               |

|-------------------------------------------------|-------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------|

| 39C, 39B                                        | ADDR00, ADDR01                                                          | TTL input | Least significant processor address bits decoded from the byte enable strobes on NT9X36BA |

| 40C,40B,<br>41C, 41B,<br>42C, 42B,<br>43C, 43B  | ADDR02, ADDR03,<br>ADDR04, ADDR05,<br>ADDR06, ADDR07,<br>ADDR08, ADDR09 | TTL input | Processor address bus from the NT9X13KA                                                   |

| 26D, 27D,<br>28D, 29D,<br>30D, 31D,<br>32D, 33D | DATA24, DATA25,<br>DATA26, DATA27,<br>DATA28, DATA29,<br>DATA30, DATA31 | TTL I/O   | Processor data bus                                                                        |

| 37B                                             | NDAS                                                                    | TTL input | Processor delayed address strobe, active low                                              |

| 36B                                             | RNW                                                                     | TTL input | Processor read/write control. low=write                                                   |

| 36C                                             | NBPRST                                                                  | TTL input | Reset from NT9X36BA, active low                                                           |

DMS-SPM Hardware Maintenance Reference Manual

(Sheet 2 of 2)

| Pin<br>number | Signal | Function  | Description                                         |

|---------------|--------|-----------|-----------------------------------------------------|

| 38C           | NMPE   | TTL input | Maintenance page enable, address strobe, active low |

| 38B           | NSPE   | TTL input | SUDS page enable, address strobe, active low        |

| 44D           | NCSEN  | TTL input | Card slot enable, active low                        |

The following table shows the network interface signal pin numbers.

| Pin number                                                   | Signal                                                                           | Function   | Description                                                                               |

|--------------------------------------------------------------|----------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------|

| 26C, 26B,<br>27C, 27B,<br>28C, 28B,<br>29C, 29B,<br>30C, 30B | RDAT0, RDAT1,<br>RDAT2, RDAT3,<br>RDAT4, RDAT5,<br>RDAT6, RDAT7,<br>RDAT8, RDAT9 | TTL output | Receive bus from paddleboard, 16 Mbit/s, 10-bit wide, PCM data bus, 2048 channel capacity |

| 31C, 31B,<br>32C, 32B,<br>33C, 33B,<br>34C, 34B,<br>35C, 35B | WBUS0, WBUS1,<br>WBUS2, WBUS3,<br>WBUS4, WBUS5,<br>WBUS6, WBUS7,<br>WBUS8, WBUS9 | TTL input  | Write bus to paddleboard, 16 Mbit/s 10-bit wide, PCM data bus, 2048 channel capacity      |

## **Power requirements**

The NT9X40DA paddleboard power requirements are itemized in the following table.

#### (Sheet 1 of 2)

| Parameter      | Minimum | Nominal | Maximum | Units | Description                                                             |

|----------------|---------|---------|---------|-------|-------------------------------------------------------------------------|

| Supply voltage | 4.75    | 5.00    | 5.25    | V     | 5.0 V TTL logic                                                         |

|                | -5.45   | -5.20   | -4.95   | V     | -5.2 V ECL logic                                                        |

|                | 3.23    | 3.30    | 3.37    | V     | QLC application specific<br>integrated circuit (ASIC)<br>supply voltage |

| Supply ripple  |         |         | 100     | mV    |                                                                         |

## NT9X40DA paddleboard (end)

### (Sheet 2 of 2)

| Parameter                 | Minimum | Nominal | Maximum | Units | Description |

|---------------------------|---------|---------|---------|-------|-------------|

| Supply current;<br>-5.2 V |         |         |         | mA    |             |

| Supply current;<br>5.0 V  |         |         |         |       |             |

| Supply current;<br>3.3 V  |         |         |         |       |             |

## NTLX50AA SPM-DMS frame assembly

## Description

In the North American market, DMS-Spectrum Peripheral Module (SPM) equipment installs in a standard DMS NTLX50AA frame assembly. The DMS NTLX50AA frame is normally provisioned to accommodate two SPM nodes, although it can be used in a single node configuration. The module allows for expansion by adding circuit packs, cabling, and power.

## ATTENTION

The NTLX50AA frame assembly is only supported by SP11 and earlier releases. For SP12 or later releases, use the NTLX91BA frame assembly.

The NTLX50AA frame assembly consists of the following features:

- standard DMS racks

- adapter brackets for dual-shelf assemblies

- cable segregation for power, fiber, signaling, and alarms

- accommodation of fiber bends of 1.5-in. radius

- front access for all cabling and maintenance activities

- retractable doors for cable protection

- covers for cable trough areas

- compatibility with DMS earthquake anchors and systems:

- earthquake-designed frame

- earthquake anchors

- earthquake bracing frames

- compatibility with overhead and under-floor DMS cabling systems

- Bellcore standards for electrostatic discharge (ESD) protection (ESD grounding is not required)

## Components

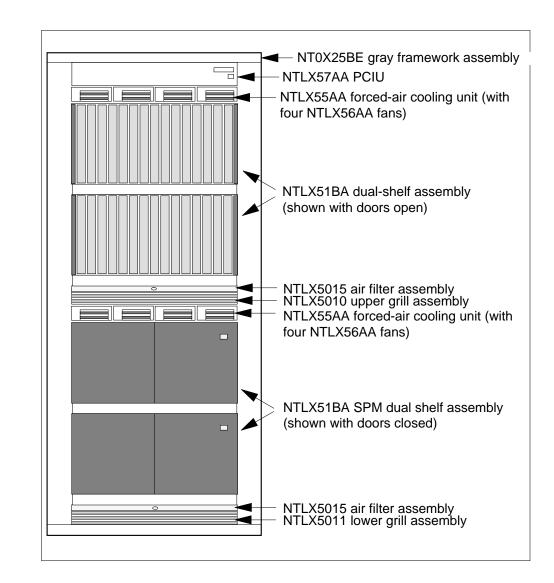

As shown in the following figure, the NTLX50AA DMS frame assembly contains the following SPM equipment and component assemblies:

- NTLX51AA or NTLX51BA dual-shelf assembly

- NTLX57AA power cabling interface unit (PCIU)

- NTLX5015 air filter

- NTLX5010 upper grill

- NTLX5011 lower grill

- NTLX55AA forced-air cooling unit

- NT0X25BE gray framework

### NTLX51AA dual-shelf assembly

One dual-shelf assembly provides 30 slots for the SPM plug-in modules. There are two NTLX51AA dual-shelf assemblies in each NTLX50AA gray framework assembly.

The NTLX51AA dual-shelf assembly accommodates the following items:

- NTLX5201 double-height backplane assembly

- NTLX5101 SPM shelf mechanical assembly (one for each dual-shelf assembly)

- NTLX5016 air-filter tray assembly

- NTLX5102 shelf-door kit

- NTLX5104 shelf cable-trough cover assembly

## NTLX51BA dual-shelf assembly

One dual-shelf assembly provides 30 slots for the SPM plug-in modules. There are two NTLX51BA dual-shelf assemblies in each NTLX50AA gray framework assembly.

The NTLX51BA dual-shelf assembly accommodates the following items:

- NTLX5211 double-height backplane assembly

- NTLX5101 SPM shelf mechanical assembly (one for each dual-shelf assembly)

- NTLX5016 air-filter tray assembly

- NTLX5102 shelf-door kit

- NTLX5104 shelf cable-trough cover assembly

## NTLX57AA PCIU assembly

The PCIU assembly accommodates a maximum of eight #6 AWG power cables from the power distribution center and 16 #10 AWG power cables for the termination of the shelf power supplies, as well as the required A and B returns.

The NTLX57AA PCIU assembly contains the following items:

- NTLX58AA alarm card assembly (one alarm card for each PCIU assembly)

- NTLX59AA fan management unit assembly (two fan management units for each PCIU assembly)

#### NTLX5015 air filter assembly

The air filter assembly filters the air supply for the NTLX51AA dual-shelf assembly. There are two NTLX5015 air-filter assemblies for each NT0X25BE gray framework assembly. The air-filter foam-element replacement part-number is A0665487.

#### NTLX5010 upper grill assembly

The upper grill assembly is located mid-point on the framework assembly. There is one NTLX5010 upper grill assembly for each NT0X25BE gray framework assembly.

#### NTLX5011 lower grill assembly

The lower grill assembly is located at the bottom of the framework assembly. There is one NTLX5011 lower grill assembly for each NT0X25BE gray framework assembly.

#### NTLX55AA cooling unit assembly

The cooling unit assembly provides mechanical ventilation for each NTLX51AA dual-shelf assembly. Each NTLX55AA cooling unit assembly contains four NTLX56AA fan assemblies.

#### NT0X25BE gray framework assembly

The NT0X25BE gray framework assembly consists of the frame that contains the built-in cable ducts, covers, and provides support for all the SPM components. There is one NT0X25BE gray framework assembly for two SPM nodes.

## Frame cabling

All the external frame cabling and all inter-assembly internal frame cabling is accessible from the front of the NTLX50BE frame assembly.

### Inter-assembly internal frame cabling

The cables listed in the following table connect the assemblies contained in the NTLX50AA frame.

| Function                         | PEC      | Connects         | То                                                    |

|----------------------------------|----------|------------------|-------------------------------------------------------|

| PCIU to SIM 1                    | NTLX5094 | NTLX57AA<br>PCIU | NTLX61AA SIM on the lower section of the bottom shelf |

| PCIU to SIM 2                    | NTLX5095 | NTLX57AA<br>PCIU | NTLX61AA SIM on the upper section of the bottom shelf |

| PCIU to SIM 3                    | NTLX5096 | NTLX57AA<br>PCIU | NTLX61AA SIM on the lower section of the top shelf    |

| PCIU to SIM 4                    | NTLX5097 | NTLX57AA<br>PCIU | NTLX61AA SIM on the upper section of the top shelf    |

| PCIU to cooling<br>unit number 1 | NTLX5098 | NTLX57AA<br>PCIU | NTLX55AA lower cooling unit assembly                  |

| PCIU to cooling<br>unit number 2 | NTLX5099 | NTLX57AA<br>PCIU | NTLX55AA upper cooling unit assembly                  |

| Frame ground cable               | NTRX1650 | NTLX50AA         | Ground                                                |

## External frame cabling

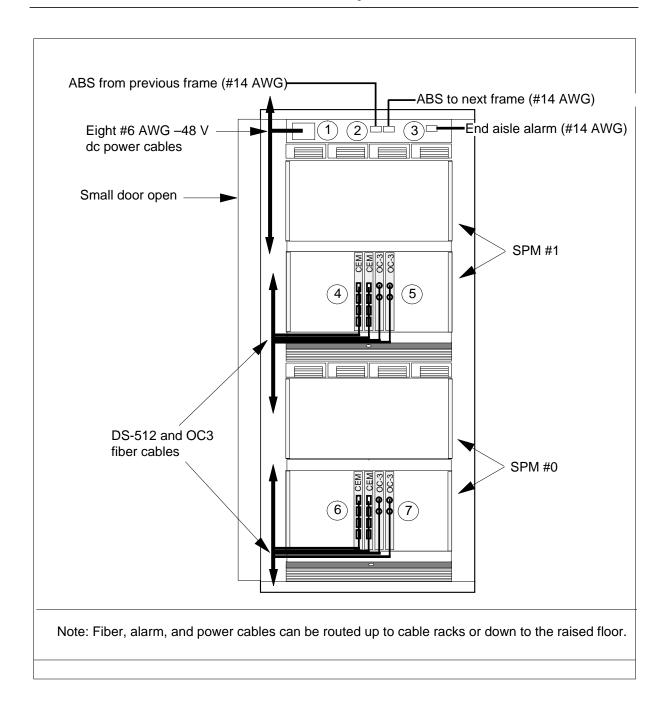

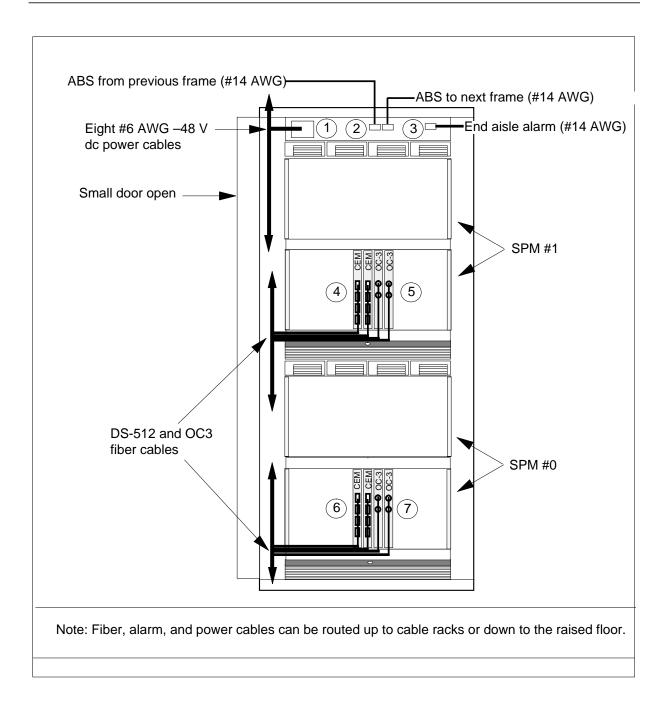

The external cables listed in the following table connect the NTLX50AA frame to other devices.

#### (Sheet 1 of 2)

| Function                                                                           | PEC           | Number<br>shown in<br>figure | Number<br>of<br>cables | Wire type | Destination                            |  |

|------------------------------------------------------------------------------------|---------------|------------------------------|------------------------|-----------|----------------------------------------|--|

| -48 V dc and -48 V<br>dc return                                                    | NPS9508-03-6  | 1                            | 8                      | #6 AWG    | Power<br>distribution<br>cabinet (PDC) |  |

| Alarm battery supply                                                               | NPS9508-03-14 | 2                            | 1                      | #14 AWG   | Next frame                             |  |

| Note: The NTLX81AA Fiber Adapter Kit is shipped loose—one kit for each OC3 module. |               |                              |                        |           |                                        |  |

#### (Sheet 2 of 2)

|                                                                                    |          | Number<br>shown in | Number<br>of |                      |                                                                   |

|------------------------------------------------------------------------------------|----------|--------------------|--------------|----------------------|-------------------------------------------------------------------|

| Function                                                                           | PEC      | figure             | cables       | Wire type            | Destination                                                       |

| End aisle alarm cable                                                              | NT0X96LX | 3                  | 1            | multiple             | End aisle alarm<br>panel (if required)                            |

| SPM frame to<br>SPM frame                                                          | NT0X96LS | not shown          | 1            | multiple             | Next SPM frame (if required)                                      |

| SPM frame to<br>DTCI frame                                                         | NT0X96LQ | not shown          | 1            | multiple             | Digital trunk<br>controller ISDN<br>(DTCI) frame (if<br>required) |

| SPM frame to<br>MSP frame                                                          | NT0X96LR | not shown          | 1            | multiple             | Modular support<br>panel (MSP)<br>frame                           |

| SPM frame to AXU                                                                   | NT0X96LT | not shown          | 1            | multiple             | Alarm<br>cross-connect<br>unit (AXU)                              |

| DS-512 from SPM<br>#1                                                              | NTLO97AW | 4                  | 4            | HCS fiber            | ENET                                                              |

| OC3 from SPM #1                                                                    | NTLX81AA | 5                  | 4            | Fiber<br>adapter kit | Fiber manager                                                     |

| DS-512 from SPM<br>#0                                                              | NTLO97AW | 6                  | 4            | HCS fiber            | ENET                                                              |

| OC3 from SPM #0                                                                    | NTLX81AA | 7                  | 4            | Fiber<br>adapter kit | Fiber manager                                                     |

| Note: The NTLX81AA Fiber Adapter Kit is shipped loose—one kit for each OC3 module. |          |                    |              |                      |                                                                   |

## **Cabling layout**

The following figure shows the cabling layout.

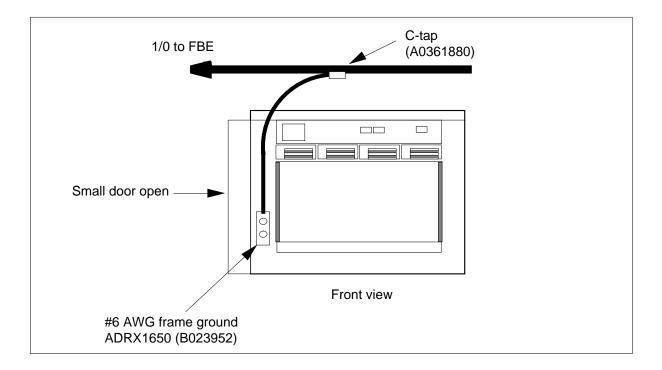

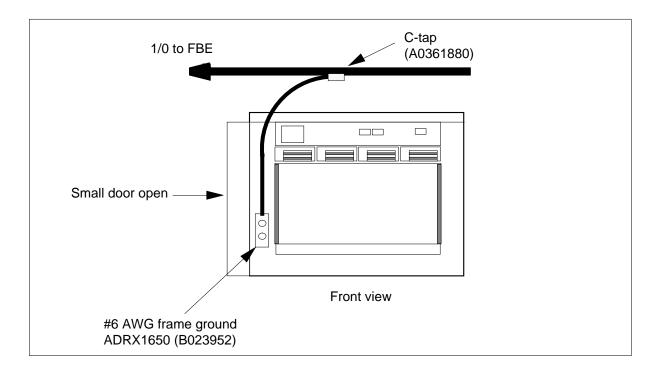

## Frame ground

The following figure shows the #6 AWG frame ground connection mounted on the left front of the NTLX50AA frame assembly. The frame ground cable requires a C-tap to a 1/0 cable connected to the frame bonding equalizer (FBE) and routed in the cable trough throughout the length of the frame line up.

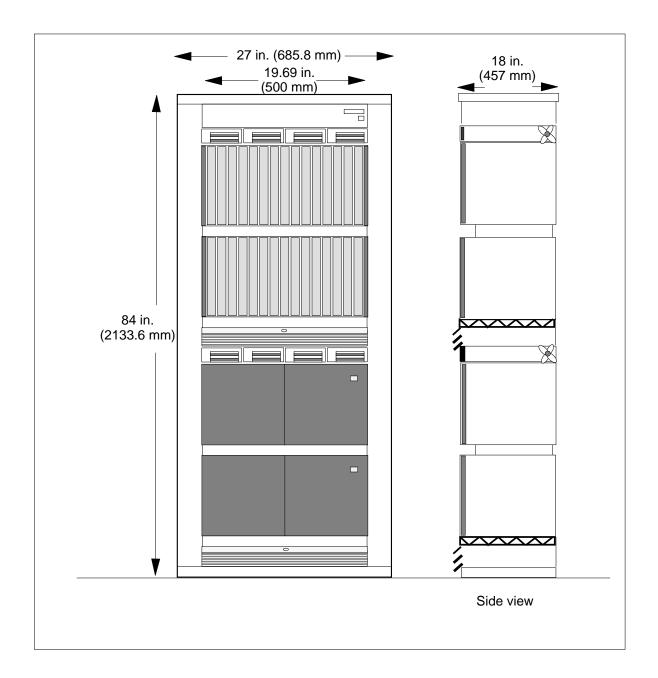

# Frame design

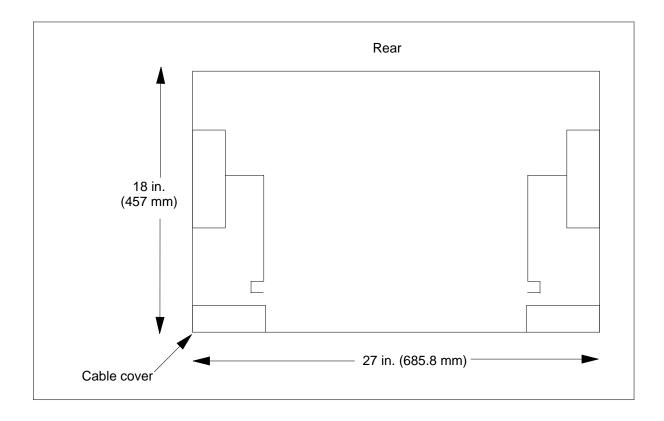

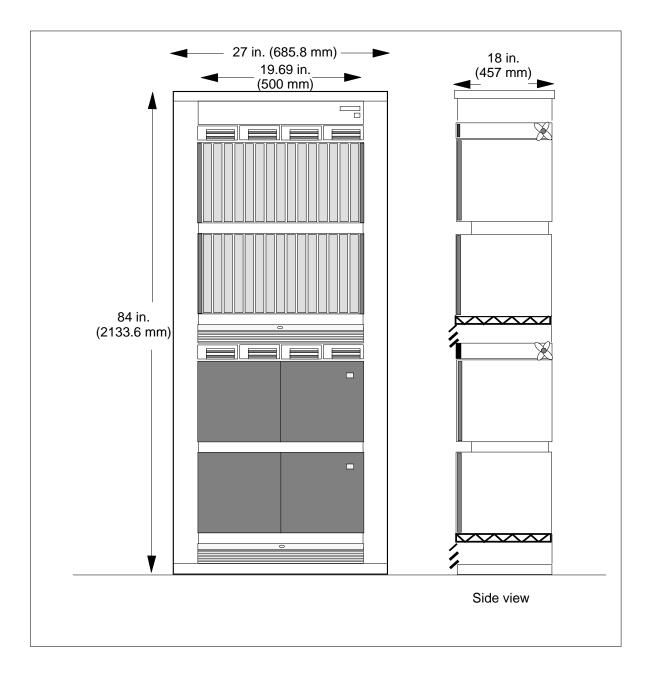

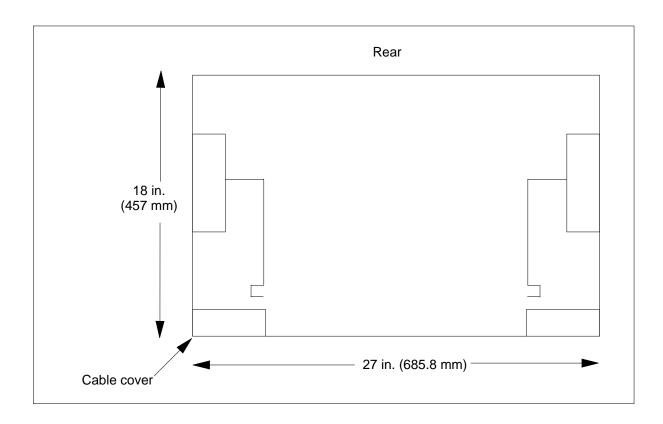

For the North American market, SPM installs in a DMS frame that measures 7 ft (2133.6 mm) x 2.25 ft (457 mm) x 1.5 ft (457 mm). The following figure shows the NTLX50AA DMS frame dimensions.

### **Floor footprint**

The following figure shows the footprint of a NTLX50AA DMS frame. The NTLX50AA frame is capable of housing two SPM nodes in this area.

# NTLX50AA SPM-DMS frame assembly (end)

# NTLX51AA dual-shelf assembly

### Description

The NTLX51AA dual-shelf assembly resides in the NTOX25BE gray framework assembly and houses the DMS-Spectrum Peripheral Module (SPM) printed circuit pack (PCP) modules.

## **Components**

The components of the the NTLX51AA dual-shelf assembly are

- NTLX5016 air filter tray assembly (one for each dual-shelf assembly)

- NTLX5101 shelf mechanical assembly (one for each dual-shelf assembly)

- NTLX5201 backplane assembly (one for each dual-shelf assembly)

- NTLX60AA blank filler faceplate (0 to 22 for each dual-shelf assembly)

- NTLX61AA shelf interface module (SIM) (two for each dual-shelf assembly)

- NTLX63AA, NTLX82AA, or NTLX82BA common equipment module (CEM) (two for each dual-shelf assembly)

Note: The NTLX63AA CEM is not compatible with SP15.

- NTLX65AA or NTLX65BA digital signal processor (DSP) resource module (RM) (0 to 24 DSP RMs for each dual-shelf assembly)

- NTLX66AA or NTLX66BA voice signal processor (VSP) RM (0 to 24 VSP RMs for each dual-shelf assembly)

*Note:* Support exists for any combination of up to 24 DSP and VSP RMs. Typically, the number of necessary DSP and VSP RMs will be less than this.

- NTLX71AA or NTLX71BA OC3 interface module (two for each dual-shelf assembly)

- NTLX72AA data link controller (DLC) RM (two for each dual-shelf assembly)

### ATTENTION

Not all modules apply to all markets.

# Design

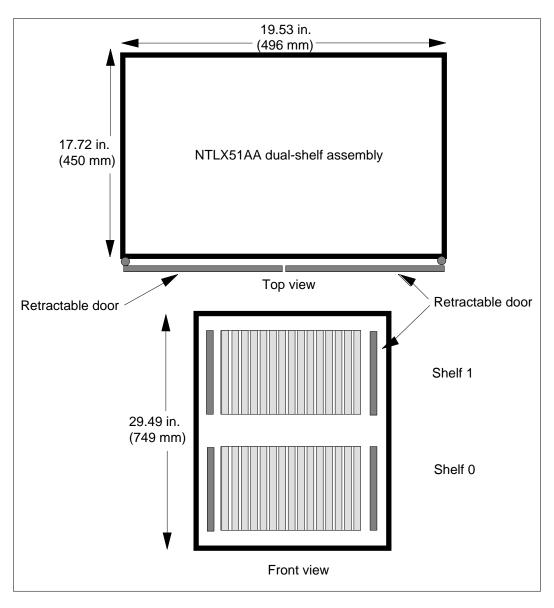

As shown in the following figure, the NTLX51AA dual-shelf assembly is 19.53 in. (496 mm) wide, 17.72 in. (450 mm) deep, and 29.49 in. (749 mm) high.

## Features

The NTLX51AA dual-shelf assembly features are

- retractable doors for cable protection

- front access of modules and connectors

- 28 module positions plus two power modules all at 1.25 in. (32 mm) pitch

- module keying that provides for 64 key positions

- backplane guide pins for module alignment

- advanced electrostatic discharge (ESD) ground to modules

# Backplane

The NTLX51AA dual-shelf assembly has a single NTLX5201 backplane and uses a five-column background connector system with male contacts on the backplane and female contacts on the plug in modules. The NTLX5201 backplane provides an eight-layer single backplane for the NTLX51AA dual-shelf assembly. The NTLX5201 backplane has the following features:

- The assembly is 19.37 in. (492 mm) high and 29.41 in. (747 mm) wide.

- The assembly is a 10-layer printed circuit board.

- The assembly has 30 card slots.

- Slots consist of a one-SU 0.1 in. (2.5 mm) 35-pin Molex connector (used specifically for power and frame ground).

- Slots consist of two-SU 0.1 in. (2.5 mm) 85-pin Molex connector (used specifically for digital signals).

- CEM slots consist of one ten-SU 0.1 in. (2.5 mm) 475-pin Molex connector (used specifically for digital signals).

## Module physical characteristics

The physical characteristics that apply to all SPM modules are described in this section. See the individual module descriptions in this manual for specific information on the electronic specifications and performance of each module.

Modules used in the SPM dual-shelf assembly have the following common physical characteristics:

- Each module is 1.22 in. (31 mm) wide, 12.4 in. (315 mm) high, and 15.75 in. (400 mm) deep.

- Modules have a minimum of 60% of the cross-sectional area open for air flow.

- Each module contains a single circuit board that is 12.01 in. (305 mm) high by 14.17 in. (360 mm) deep.

- Modules that require external optical or electical cable connections have cable connectors on the front panel.

- Modules weigh 9 lbs (4 kg) or less.

- Module packaging provides EMI and EMC shielding of 55 db up to 1 GHz.

- Modules can dissipate up to 55 W of power by allowing 150 linear ft/min (7.5 m/s) of air flow through the module.

## **Module Location**

The following figure shows the NTLX51AA dual-shelf assembly module locations with module slot locations.

### CAUTION

Air and electro-magnetic interference integrity Slots that do not contain an RM must have filler modules installed to maintain air and electro-magnetic interference

The NTLX51AA dual-shelf assembly has a maximum of 30 card slots

The NTLX51AA dual-shelf assembly has a maximum of 30 card slots available for peripheral and system support modules. The NTLX51AA dual-shelf assembly must have the following provisioned modules:

- NTLX61AA SIM A and SIM B located in slot A, at right-hand end of shelf 0 and shelf 1.

- NTLX71AA or NTLX71BA OC3 interface modules located in slots 9 and 10 of shelf 0.

- NTLX63AA, NTLX82AA, or NTLX82BA CEM 0 and CEM 1 located in slots 7 and 8 of shelf 0.

Note: The NTLX63AA CEM is not compatible with SP15.

• With the remaining 24 slots provisioned according to specific applications.

The NTLX51AA dual-shelf assembly limits the CEM and OC3 interface modules to specific slot locations because of the additional communications resources needed by the modules.

The OC3 interface modules use slots 9 and 10 because of their bandwidth requirements. These slots have six extra links that provide two additional S-link clusters, delivering full-bandwidth-payload termination for OC3.

The recommended position of the DLC RMs is in slots 1 and 7 of shelf 1.

The DSP RMs and VSP RMs are permitted in all slots that are not reserved for system-level modules (SIM, CEM, or OC3 modules).

*Note:* All modules may not apply to all markets.

### **Available S-links**

S-links are available to card slots as follows:

- Slots 9 and 10 on the lower shelf each provide 9 S-links

- All other slots each provide 3 S-links

The following figure shows the number of S-links available at the card slot (inside the dual-shelf assembly).

| Shelf 0 |                |          | Shelf 1        |

|---------|----------------|----------|----------------|

| 01      | RM (3 S-links) | 9        | RM (3 S-links) |

| 02      | RM (3 S-links) | 02       | RM (3 S-links) |

| 03      | RM (3 S-links) | 03       | RM (3 S-links) |

| 04      | RM (3 S-links) | 04       | RM (3 S-links) |

| 5       | RM (3 S-links) | <b>B</b> | RM (3 S-links) |

| 6       | RM (3 S-links) | 06       | RM (3 S-links) |

| 07      | CEM NTLX63AA   | 70       | RM (3 S-links) |

| 80      | CEM NTLX63AA   | 80       | RM (3 S-links) |

| 60      | IM (9 S-links) | 60       | RM (3 S-links) |

| 10      | IM (9 S-links) | 10       | RM (3 S-links) |

| 1       | RM (3 S-links) | 1 ±      | RM (3 S-links) |

| 12      | RM (3 S-links) | 12       | RM (3 S-links) |

| 13      | RM (3 S-links) | 13       | RM (3 S-links) |

| 14      | RM (3 S-links) | 14       | RM (3 S-links) |

| A       | SIM NTL61AA    | ≻        | SIM NTL61AA    |

The following table describes the NTLX51AA dual-shelf assembly resource modules, system modules, and the enhanced network (ENET) NT9X40DA paddleboard.

DMS-SPM Hardware Maintenance Reference Manual

NTLX51AA dual-shelf assembly (continued)

Hardware descriptions 3-25

| PEC                                | Slot/shelf                     | Description                                        |

|------------------------------------|--------------------------------|----------------------------------------------------|

| NT9X40DA                           | Resides in ENET                | ENET quad DS-512S fiber link interface paddleboard |

| NTLX61AA                           | Slot 15/shelf 0,               | SIM                                                |

|                                    | Slot 15/shelf 1                |                                                    |

| NTLX63AA,<br>NTLX82AA,<br>NTLX82BA | Slots 7 and 8/shelf 0          | CEM                                                |

| NTLX65AA,<br>NTLX65BA              | Slots 9-13/shelf 1             | DSP RM                                             |

| NTLX66AA,                          | Slots 3, 4, and 11-14/shelf 0, | VSP RM                                             |

| NTLX66BA,<br>NTLX85AA,<br>NTLX86AA | Slots 5, 6, and 14/shelf 1     |                                                    |

| NTLX71AA,<br>NTLX71BA              | Slots 9 and 10/shelf 0         | OC3 interface module                               |

| NTLX72AA                           | Slots 1 and 7/shelf 1          | DLC RM                                             |

The NT9X40DA paddleboard resides in the ENET and connects to the SPM equipment through fiber-optic interconnects.

Note 1: The NTLX63AA CEM is not compatible with SP15.

*Note 2:* The quantities and locations of DSP and VSP RMs are office dependent.

*Note 3:* All modules may not apply to all markets.

### **RM** capacities

The actual provisioning for DSP RM and VSP RM is application dependent. The following tables show the islands' capacities for each service used within an application.

### ATTENTION

The voice signal processor (VSP) does not apply to all markets.

# NTLX51AA dual-shelf assembly (end)

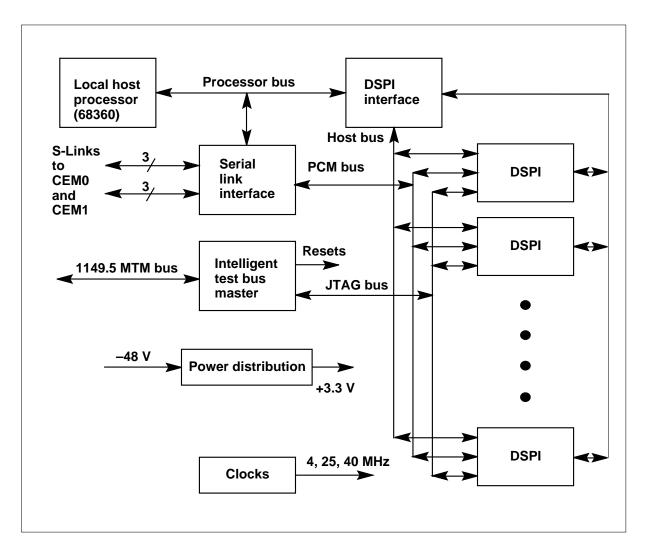

Each DSP RM provides nine DSP islands (DSPI). Each of the nine islands on a DSP RM can be configured for a different application. A single DSPI can provide only one type of service application at any given time.

| DSP RM application (function)           | Quantity per DSPI |

|-----------------------------------------|-------------------|

| Tone synthesizer (TONESYN)              | 255               |

| Multi frequency receiver (MF)           | 40                |

| Continuity tone transceiver (COT)       | 80                |

| DTMF receiver with dial tone generation | 64                |

| AB bit handler (ABBH)                   | 14                |

Each VSP RM provides 10 turbo DSP islands (tDSPI).

| VSP RM application (function) | Quantity per tDSPI |

|-------------------------------|--------------------|

| Echo canceller (ECAN)         | 26                 |

## NTLX51BA dual-shelf assembly

#### Description

The NTLX51BA dual-shelf assembly resides in the NTOX25BE gray framework assembly and houses the DMS-Spectrum Peripheral Module (SPM) printed circuit pack (PCP) modules.The NTLX51BA dual-shelf assembly is a replacement for the NTLX51AA dual-shelf assembly.

The following are the enhancements available when NTLX51AA is upgraded to the NTLX51BA:

- The NTLX51BA dual-shelf assembly provides four high speed slots to accomodate resource modules (RMs) that have high bandwidth needs, while the NTLX51AA dual-shelf assembly only provides two.

- The NTLX51BA provides four low speed slots to accomodate RMs that have low bandwidth needs, while the NTLX51AA provides none.

### Components

The components of the the NTLX51BA dual-shelf assembly are

- NTLX5016 air filter tray assembly (one for each dual-shelf assembly)

- NTLX5101 shelf mechanical assembly (one for each dual-shelf assembly)

- NTLX5211 backplane assembly (one for each dual-shelf assembly)

- NTLX60AA blank filler faceplate (0 to 22 for each dual-shelf assembly)

- NTLX61AA shelf interface module (SIM) (two for each dual-shelf assembly)

- NTLX63AA, NTLX82AA, or NTLX82BA common equipment module (CEM) (two for each dual-shelf assembly)

*Note:* The NTLX63AA CEM is not compatible with SP15.

- NTLX65AA or NTLX65BA digital signal processor (DSP) resource module (RM) (0 to 24 DSP RMs for each dual-shelf assembly)

- NTLX66AA, NTLX66BA, NTLX85AA, or NTLX86AA voice signal processor (VSP) RM (0 to 24 VSP RMs for each dual-shelf assembly)

*Note:* Support exists for any combination of up to 24 DSP and VSP RMs. Typically, the number of necessary DSP and VSP RMs will be less than this.

- NTLX71AA or NTLX71BA OC3 interface module (0 or 2 for each dual-shelf assembly)

- NTLX72AA data link controller (DLC) RM (0 or 2 DLC RMs for each dual-shelf assembly)

### ATTENTION

Not all modules apply to all markets.

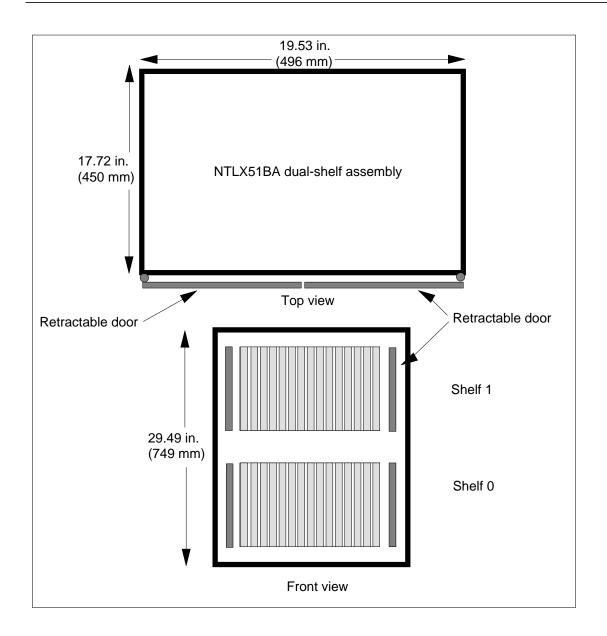

## Design

As shown in the following figure, the NTLX51BA dual-shelf assembly is 19.53 in. (496 mm) wide, 17.72 in. (450 mm) deep, and 29.49 in. (749 mm) high.

## **Features**

The NTLX51BA dual-shelf assembly features are

- retractable doors for cable protection

- front access of modules and connectors

- 28 module positions plus two power modules all at 1.25 in. (32 mm) pitch

- module keying that provides for 64 key positions

- backplane guide pins for module alignment

- advanced electrostatic discharge (ESD) ground to modules

# Backplane

The NTLX51BA dual-shelf assembly has a single NTLX5211 backplane and uses a five-column background connector system with male contacts on the backplane and female contacts on the plug in modules. The NTLX5211 backplane provides a ten-layer single backplane for the NTLX51BA dual-shelf assembly. The NTLX5211 backplane has the following features:

- The assembly is 19.37 in. (492 mm) high and 29.41 in. (747 mm) wide.

- The assembly is a 10-layer printed circuit board.

- The assembly has 30 card slots.

- Slots consist of a one-SU 0.1 in. (2.5 mm) 35-pin Molex connector (used specifically for power and frame ground).

- Slots consist of two-SU 0.1 in. (2.5 mm) 85-pin Molex connector (used specifically for digital signals).

- CEM slots consist of one ten-SU 0.1 in. (2.5 mm) 475-pin Molex connector (used specifically for digital signals).

# Module physical characteristics

The physical characteristics that apply to all SPM modules are described in this section. See the individual module descriptions in this manual for specific information on the electronic specifications and performance of each module.

Modules used in the SPM dual-shelf assembly have the following common physical characteristics:

- Each module is 1.22 in. (31 mm) wide, 12.4 in. (315 mm) high, and 15.75 in. (400 mm) deep.

- Modules have a minimum of 60% of the cross-sectional area open for air flow.

- Each module contains a single circuit board that is 12.01 in. (305 mm) high by 14.17 in. (360 mm) deep.

- Modules that require external optical or electical cable connections have cable connectors on the front panel.

- Modules weigh 9 lbs (4 kg) or less.

- Module packaging provides EMI and EMC shielding of 55 db up to 1 GHz.

- Modules can dissipate up to 55 W of power by allowing 150 linear ft/min (7.5 m/s) of air flow through the module.

## **Module Location**

The following figure shows the NTLX51BA dual-shelf assembly module locations with module slot locations.

#### CAUTION

Air and electro-magnetic interference integrity

Slots that do not contain an RM must have filler modules installed to maintain air and electro-magnetic interference integrity.

The NTLX51BA dual-shelf assembly has a maximum of 30 card slots available for peripheral and system support modules. The NTLX51BA dual-shelf assembly must have the following provisioned modules:

- NTLX61AA SIM A and SIM B located in slot A, at right-hand end of shelf 0 and shelf 1.

- NTLX71AA or NTLX71BA OC3 interface modules located in slots 9 and 10 of shelf 0.

- NTLX63AA, NTLX82AA, or NTLX82BA CEM 0 and CEM 1 located in slots 7 and 8 of shelf 0.

*Note:* The NTLX63AA CEM is not compatible with SP15.

• With the remaining 24 slots provisioned according to specific applications.

The NTLX51BA dual-shelf assembly limits the CEM and the OC3 interface modules to specific slot locations because of the additional communications resources needed by the modules.

A pair of OC3 interface modules (one active and one spare) uses slots 9 and 10 of shelf 0 because of bandwidth requirements. These high-speed slots have additional bandwidth to satisfy the bandwidth requirements of the OC3.

The recommended position of the DLC RMs is in slots 1 and 7 of shelf 1.

The DSP RMs and VSP RMs are permitted in all slots that are not reserved for system-level modules (SIM, CEM, and OC3).

*Note:* All modules may not apply to all markets.

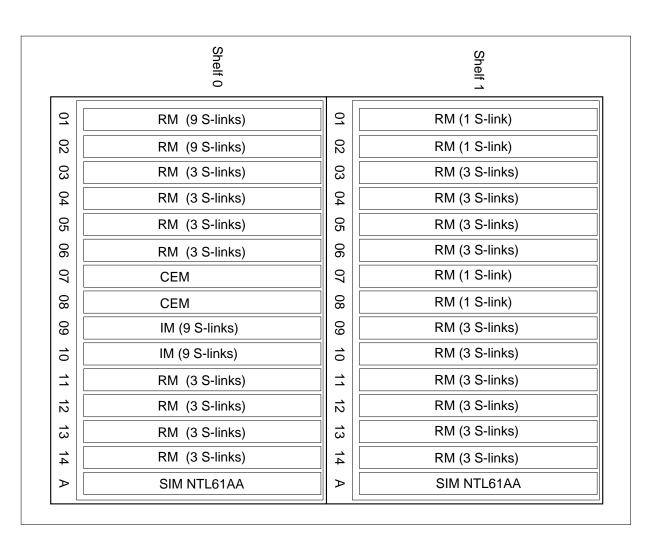

# **Available S-links**

S-links are available to card slots as follows:

- Slots 1, 2, 7, and 8 on the upper shelf each provide 1 S-link

- Slots 1, 2, 9 and 10 on the lower shelf each provide 9 S-links

- All other slots each provide 3 S-links

The following figure shows the number of S-links available at each card slot inside the high speed dual-shelf assembly.

paddleboard. The following table describes the NTLX51BA dual-shelf assembly resource modules, system modules, and the enhanced network (ENET) NT9X40DA

NTLX51BA dual-shelf assembly (continued)

| PEC                                | Slot/shelf                     | Description                                        |

|------------------------------------|--------------------------------|----------------------------------------------------|

| NT9X40DA                           | Resides in ENET                | ENET quad DS-512S fiber link interface paddleboard |

| NTLX61AA                           | Slot 15/shelf 0,               | SIM                                                |

|                                    | Slot 15/shelf 1                |                                                    |

| NTLX63AA,<br>NTLX82AA,<br>NTLX82BA | Slots 7 and 8/shelf 0          | CEM                                                |

| NTLX65AA,<br>NTLX65BA              | Slots 9-13/shelf 1             | DSP RM                                             |

| NTLX66AA,                          | Slots 3, 4, and 11-14/shelf 0, | VSP RM                                             |

| NTLX66BA,<br>NTLX85AA,<br>NTLX86AA | Slots 5, 6, and 14/shelf 1     |                                                    |

| NTLX71AA,<br>NTLX71BA              | Slots 9 and 10/shelf 0         | OC3 interface module                               |

| NTLX72AA                           | Slots 1 and 7/shelf 1          | DLC RM                                             |

The NT9X40DA paddleboard resides in the ENET and connects to the SPM equipment through fiber-optic interconnects.

Note 1: The NTLX63AA CEM is not compatible with SP15.

*Note 2:* The quantities and locations of DSP and VSP RMs are office dependent.

*Note 3:* All modules may not apply to all markets.

## **RM** capacities

The actual provisioning for DSP RM and VSP RM is application dependent. The following tables show the islands' capacities for each service used within an application.

### ATTENTION

The voice signal processor (VSP) does not apply to all markets.

# NTLX51BA dual-shelf assembly (end)

Each DSP RM provides nine DSP islands (DSPI). Each of the nine islands on a DSP RM can be configured for a different application. A single DSPI can provide only one type of service application at any given time.

| DSP RM application (function)           | Quantity per DSPI |

|-----------------------------------------|-------------------|

| Tone synthesizer (TONESYN)              | 255               |

| Multi frequency receiver (MF)           | 40                |

| Continuity tone transceiver (COT)       | 80                |

| DTMF receiver with dial tone generation | 64                |

| AB bit handler (ABBH)                   | 14                |

Each VSP RM provides 10 turbo DSP islands (tDSPI).

| VSP RM application (function) | Quantity per tDSPI |

|-------------------------------|--------------------|

| Echo canceller (ECAN)         | 26                 |

# NTLX55AA cooling unit and grill assemblies

## Description

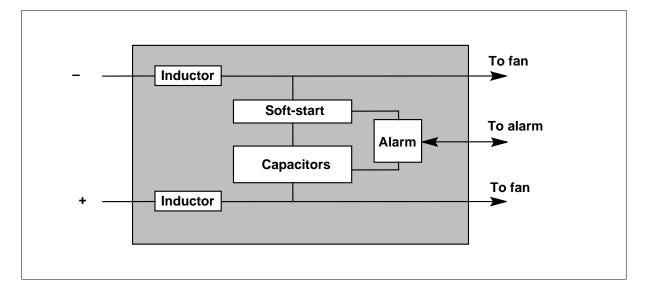

The DMS-Spectrum Peripheral Module (SPM) NTLX55AA cooling unit provides

- the basic sheet metal mounts for four NTLX56AA fan units and a grill assembly

- the necessary support electronics for operation and alarms

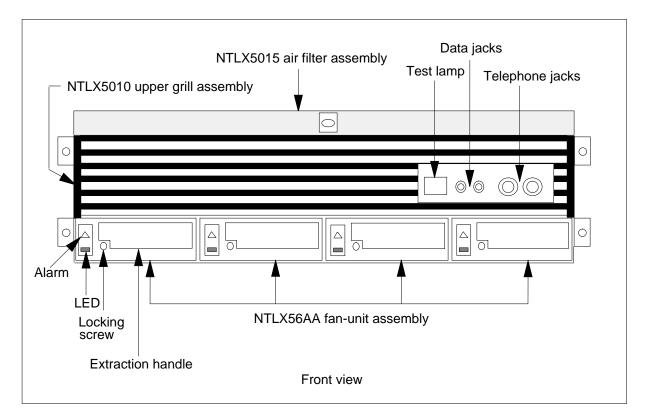

One NTLX55AA cooling unit is required for each NTLX51AA or NTLX51BA dual-shelf assembly. The following figure shows the NTLX55AA cooling unit, its location, the NTLX5010 upper grill assembly, and an NTLX5015 air filter assembly.

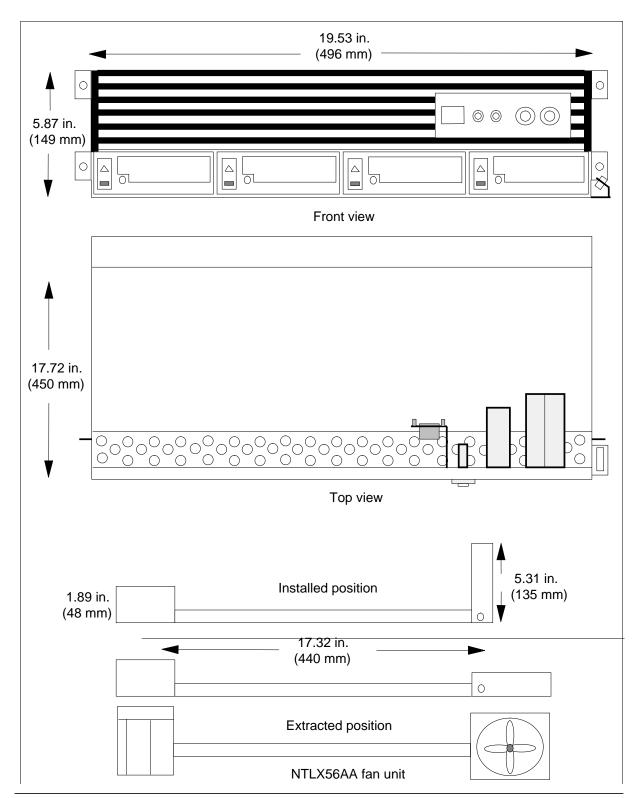

As shown in the following figure, the NTLX55AA cooling unit and NTLX5110 upper grill assembly is 19.53 in. (496 mm) wide, 5.87 in. (149 mm) high, and 17.72 in. (450 mm) deep.

# NTLX55AA cooling unit and grill assemblies (continued)

297-1771-550 Standard 05.02 April 2001

# Components

### **Cooling unit**

The cooling unit provides

- four replaceable NTLX56AA fan units

- a baffle for airflow management

- front access to the fan units

- fan power-termination and alarm interfaces

- sufficient airflow to maintain cooling effectiveness if a single fan fails

### **Cooling air filtration**

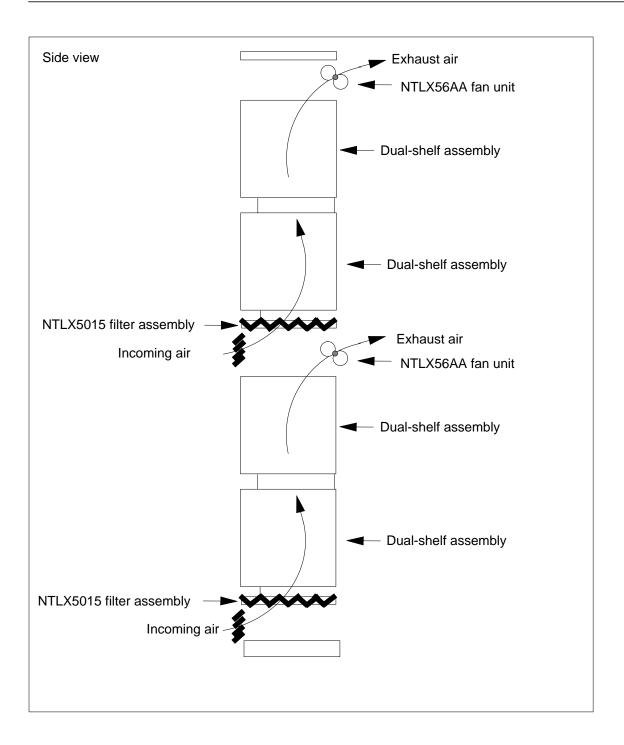

As shown in the following figure, the NTLX5015 filter assembly rests horizontally at the bottom of each NTLX51AA or NTLX51BA dual-shelf assembly. The foam air filter elements contained in the NTLX5015 assembly are not reusable. Replace the filter periodically, depending on the local dust conditions. The foam filter-element part number is A0665487.

### **Grill assemblies**

Grill assemblies protect the ambient air intakes that cool the dual-shelf assembly. As shown in the following figure, the bottom dual-shelf assembly draws air through the NTLX5011 lower grill assembly mounted in the bottom of the frame. The upper dual-shelf assembly draws cooling air through the NTLX5010 upper grill assembly located between the dual-shelf assemblies.

The fans draw air through the grills, into the NTLX5015 air filter assemblies, and then into the actual shelves for cooling. The fans expel the air to the rear of the frame assembly.

### Fan unit

The NTLX56AA fan units are individually replaceable fans that include mounting slides and connectors. The NTLX56AA fan units are removed by turning the plastic screw clockwise (located on the extraction handle) and pulling the unit out of the NTLX55AA cooling assembly.

# NTLX55AA cooling unit and grill assemblies (end)

# NTLX57AA PCIU

## Description

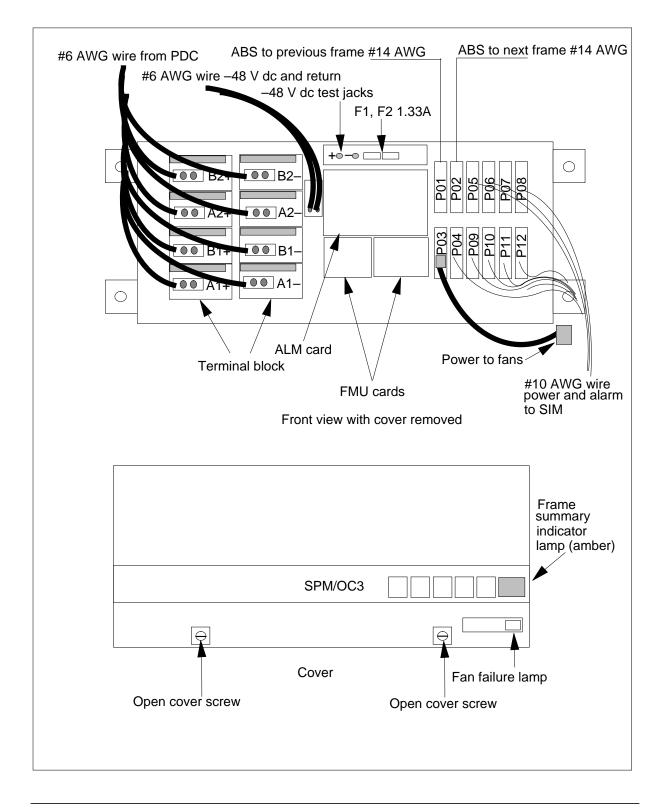

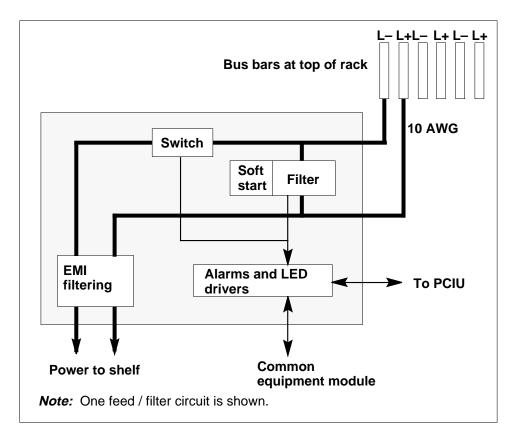

The NTLX57AA power cabling interface unit (PCIU), shown in the following figure, is located in a frame power distribution tray and mounted at the top of the NTOX25BE gray framework assembly. It serves as a central distribution and gathering point for all power and alarm cabling used within the framework assembly of the DMS-Spectrum Peripheral Module (SPM). The NTLX57AA PCIU provides a connection point for the #6 AWG power feed cables from the power distribution center and power and alarm cables, #10 AWG wires, to the NTLX61AA shelf interface modules (SIM) and NTLX55AA cooling units. The NTLX57AA PCIU contains a NTLX58AA alarm card assembly (ALM) and two NTLX59AA fan management units (FMU). A #14 AWG wire from the previous framework assembly with alarm battery supply (ABS) is terminated at P01 (see the following illustration) and sent to the next framework assembly through a #14 AWG wire from P02.

When the frame summary indicator (amber lamp) located on the front cover is off, there are no active alarm in the frame. When the amber lamp is on, there is an active alarm in the frame.

The NTLX57AA PCIU provides the following:

- accommodates up to eight #6 AWG power cables from power distribution center (PDC) and return A (-48 V dc) and B feeds (-48 V dc return)

- accommodates up to sixteen #10 AWG power cables for termination to shelf supply and return A and B feeds

- provides ABS for telephone/data jacks, frame fail LED, and end of aisle LED termination

- provides alarm links to each NTLX51AA or NTLX51BA dual-shelf assembly

- provides -48V dc power (A and B feed) to each NTLX55AA cooling unit

- allows front access to all connections for installation and maintenance

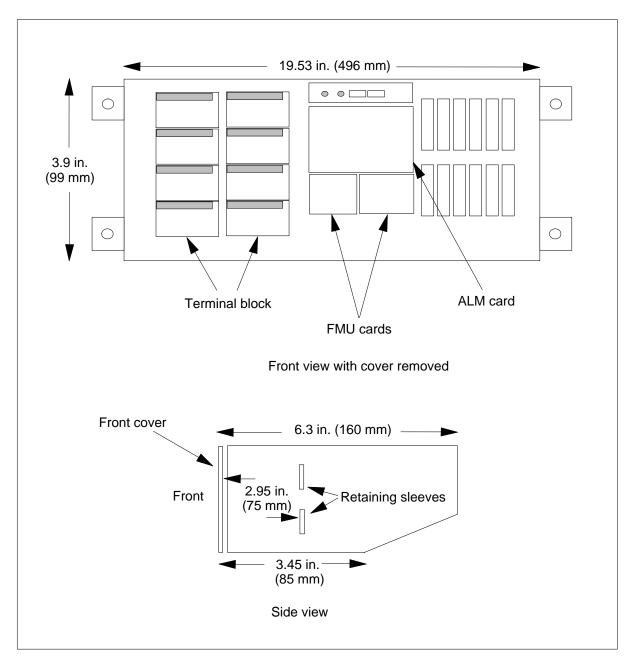

As shown in the following figure, the NTLX57AA PCIU is 19.53 in. (496 mm) wide, 3.9 in. (99 mm) high, and 6.3 in. (160 mm) deep. The retaining sleeves are 2.95 in. (75 mm) from the front of the NTLX57AA PCIU.

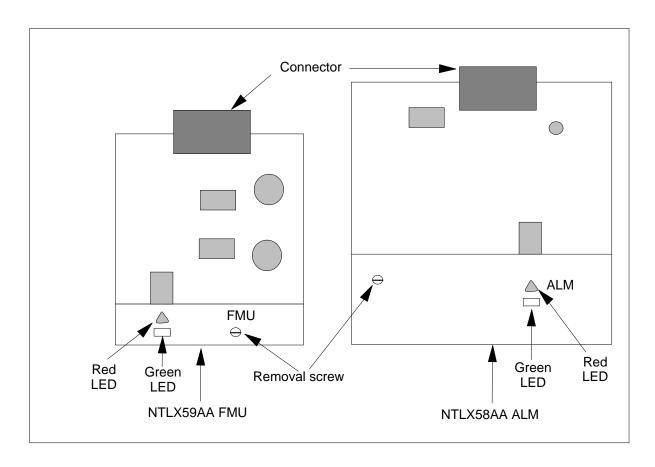

The following figure shows the NTLX58AA ALM and NTLX59AA FMU (PCIU contains two FMUs), which are located in the NTLX57AA PCIU. These three subassemblies are field replaceable components.

# NTLX58AA ALM module functions

The following are the main functions of the NTLX58AA ALM module:

- monitor a maximum of four SIMs

- monitor a maximum of two fan filters

- monitor a maximum of two NTLX55AA cooling units

- provide control for all the fan LEDs

- monitor ABS fuse failures

- report alarms on all NTLX51AA or NTLX51BA dual-shelf assemblies

- report rack failure and PCIU failure indications

- forward major alarm reports to the office alarm unit

### ALM module functional blocks

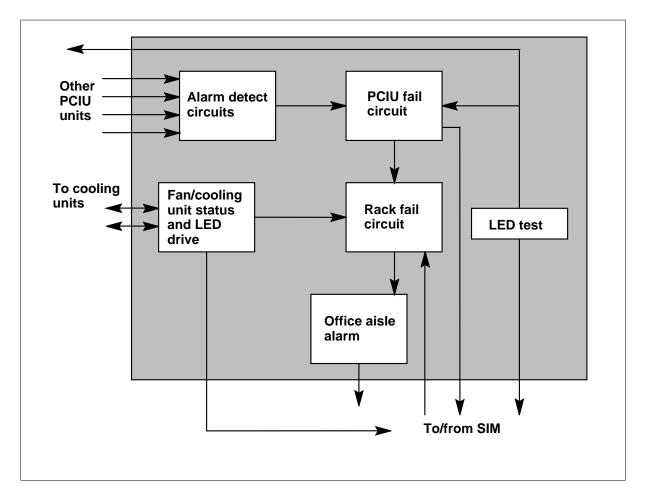

NTLX58AA ALM module has the following functional blocks:

- alarm detection circuits

- PCIU fail circuit

- fan/cooling unit status and LED drive

- rack fail circuit

- LED test

- office aisle alarm

The following figure shows the NTLX58AA ALM module functional block diagram.

#### Alarm detection

The alarm detection function accepts alarms from other NTLX57AA PCIUs and the LED test function. It forwards the composite alarm to the PCIU fail circuitry and to the PCIU shelf for further processing.

#### PCIU fail circuit

The rack fail function combines the PCIU fail signals with the fan/cooling unit status input. The composite signal is applied to the office aisle alarm block for delivery to the row-end alarm display and to the office alarm device.

#### Fan/cooling unit status and LED drive

Eight fan/cooling unit status and alarms are combined by this function and forwarded to the shelf and to the rack fail circuitry for further processing.

#### Rack fail circuit

The rack fail circuitry accepts alarm signals from the PCIU fail circuit, the fan/cooling unit status and LED drive function, and from a shelf-level alarm signal. The rack fail circuitry provides alarm input to the office aisle alarm circuitry.

#### LED test

The LED test function lights the LEDs. It also provides a signal to the dual-shelf assembly that indicates that the LEDs are being tested.

#### Office aisle alarm

Rack fail and PCIU fail indicators are also driven automatically for PCIU failures or when requested by the shelf. There are two external visual indicators driven by the alarm module: the rack fail LEDs and the PCIU fail LEDs. In addition, the alarm module generates a 10-second (approximate) LED TEST signal when it is activated by a momentary-contact external switch.

#### Signaling for the NTLX58AA ALM module

The following table shows the signaling and functioning for the NTLX58AA ALM module.

| Pin number | Signal  | Function | Comments                           |

|------------|---------|----------|------------------------------------|

| 2A         | BIPFAIL | output   | OC (-48/-60 V dc)> 0 V dc on alarm |

| 2B         | AISALM2 | output   | AISNO> AISALM1 on alarm            |

| 2C         | AISALM1 | output   | AISNO> AISALM2 on alarm            |

| (Sheet | 1 | of | 3) |

|--------|---|----|----|

|--------|---|----|----|

| (Sheet 2 of 3) |            |          |                                    |

|----------------|------------|----------|------------------------------------|

| Pin number     | Signal     | Function | Comments                           |

| 2D             | L+(ABS)    | input    | 0 V dc (1.33 A max)                |

| 2E             | L+(ABS)    | input    | 0 V dc (1.33 A max)                |

| 3C             | AISNO      | output   | AISALM1> AISALM2 on alarm          |

| 3D             | FLTALM1    | input    | 0 V dc> OC (18V dc) on alarm       |

| 3E             | FLTALM2    | input    | 0 V dc> OC (18V dc) on alarm       |

| 4C             | LEDTEST    | input    | -48/-60 V dc> 0 V dc on TEST       |

| 4D             | CUFAIL2    | output   | 0 V dc> OC (18 V dc) on alarm      |

| 4E             | CUFAIL2    | output   | 0 V dc> OC (18 V dc) on alarm      |

| 5B             | FOLLOWLED4 | input    | 0 V dc> OC (18 V dc) on alarm      |

| 5C             | FOLLOWLED3 | input    | 0 V dc> OC (18 V dc) on alarm      |

| 5D             | FOLLOWLED2 | input    | 0 V dc> OC (18 V dc) on alarm      |

| 5E             | FOLLOWLED1 | input    | 0 V dc> OC (18 V dc) on alarm      |