# **Critical Release Notice**

Publication number: 297-5001-548 Publication release: Standard 12.02

# The content of this customer NTP supports the SN06 (DMS) and ISN06 (TDM) software releases.

Bookmarks used in this NTP highlight the changes between the baseline NTP and the current release. The bookmarks provided are color-coded to identify release-specific content changes. NTP volumes that do not contain bookmarks indicate that the baseline NTP remains unchanged and is valid for the current release.

# **Bookmark Color Legend**

Black: Applies to new or modified content for the baseline NTP that is valid through the current release.

Red: Applies to new or modified content for NA017/ISN04 (TDM) that is valid through the current release.

Blue: Applies to new or modified content for NA018 (SN05 DMS)/ISN05 (TDM) that is valid through the current release.

Green: Applies to new or modified content for SN06 (DMS)/ISN06 (TDM) that is valid through the current release.

*Attention! Adobe* @ *Acrobat* @ *Reader*  $^{TM}$  5.0 *is required to view bookmarks in color.*

# **Publication History**

# March 2004

Standard release 12.02 for software release SN06 (DMS) and ISN06 (TDM).

Card NT9X30AB is Manufacture Discontinued and is replaced by new card NT9X30AC.

# 297-5001-548

DMS-100 Family

# DMS SuperNode and DMS SuperNode SE Computing Module

CM Maintenance Guide

BASE14 Standard 12.01 March 3, 2000

# DMS-100 Family DMS SuperNode and DMS SuperNode SE Computing Module

CM Maintenance Guide

Publication number: 297-5001-548 Product release: BASE14 Document release: Standard 12.01 Date: March 3, 2000

Copyright © 1993, 1994, 1995, 1996, 1997, 1998, 1999, 2000 Nortel Networks, All Rights Reserved

Printed in the United States of America

**NORTEL NETWORKS CONFIDENTIAL:** The information contained herein is the property of Nortel Networks and is strictly confidential. Except as expressly authorized in writing by Nortel Networks, the holder shall keep all information contained herein confidential, shall disclose the information only to its employees with a need to know, and shall protect the information, in whole or in part, from disclosure and dissemination to third parties with the same degree of care it uses to protect its own confidential information, but with no less than reasonable care. Except as expressly authorized in writing by Nortel Networks, the holder is granted no rights to use the information contained herein.

Information is subject to change without notice. Northern Telecom reserves the right to make changes in design or components as progress in engineering and manufacturing may warrant.

DMS, MAP, NORTEL, NORTEL NETWORKS, NORTHERN TELECOM, NT, and SUPERNODE are trademarks Northern Telecom.

# **Publication history**

| March 2000   |                                                               |

|--------------|---------------------------------------------------------------|

|              | BASE14 Standard 12.01                                         |

|              | • updated MMINFO in "User interface and commands" chapter     |

| August 1999  | BASE13 Standard 11.01                                         |

|              | • add MTCTST to "Preventative maintenance strategies" chapter |

|              | • add MTCTST to "Trouble isolation tools" chapter             |

| April 1999   | BASE10 Standard 10.03                                         |

|              | • editing changes requested by NTJI.                          |

| June 1998    | BASE10 Standard 10.02                                         |

|              | • editing changes                                             |

| February 199 | <b>B</b> ASE10 Standard 10.01                                 |

|              | For feature SR7066, added information on the following cards: |

|              | • NT9X10DA processor card (Chapters 1, 2, and 6)              |

|              | • NT9X14FA memory card (Chapters 1, 5, and 8)                 |

|              | • NT9X26GA RT1F card (Chapters 6)                             |

|              |                                                               |

| iv           |                                                                                                                                                                   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 19  | <b>97</b><br>BASE09 Standard 09.02                                                                                                                                |

|              | editing changes                                                                                                                                                   |

| August 1997  | BASE09 Standard 09.01                                                                                                                                             |

|              | • revisions to Chapters 5 and 9 for feature CM0902                                                                                                                |

| May 1997     | BASE08 Standard 08.02                                                                                                                                             |

|              | • technical edit changes to Chapter 8                                                                                                                             |

| March 1997   | BASE08 Standard 08.01                                                                                                                                             |

|              | • revisions associated with the following features:                                                                                                               |

|              | — CM0801 (Chapter 3, "Logs")                                                                                                                                      |

|              | <ul> <li>SR0075 (Chapter 1, "Overview"; Chapter 2 "Preventive maintenance";<br/>Chapter 5, "User interface"; and Chapter 6, "Cards and paddle boards")</li> </ul> |

|              | • addition of StrAlc alarm triggers to Chapter 8 ("Troubleshooting charts")                                                                                       |

|              | • revision of MemLim alarm trigger points in Chapter 8                                                                                                            |

|              | <ul> <li>addition of detailed descriptions of the LowMem, StrAlc, LOWSpr,<br/>LowSpr, MemLim, SLMLIM, and SLMLim alarms</li> </ul>                                |

| November 19  | 96<br>BASE07 Standard 07.03                                                                                                                                       |

|              | • changes associated with PRS CM60296                                                                                                                             |

| September 19 | 996<br>BASE07 Standard 07.02                                                                                                                                      |

|              | • editing and verification changes to chapter 5                                                                                                                   |

|              | • addition of missing command parameter information to chapter 5                                                                                                  |

# August 1996

BASE07 Standard 07.01

- revisions associated with the new CM RExFlt alarm

- revisions associated with the critical REx test disable feature

## November 1995

CSP05 Standard 06.01

- added new chapter "Mismatch analysis"

- added feature information to the "Overview" chapter

- added feature information to the "Preventive maintenance strategies" chapter

- added feature information to the "Logs" chapter

- added feature information to the "User interface and commands" chapter

- added feature information to the "Cards and paddle boards" chapter

- reference to BCSMON changed to DMSMON in the "Trouble isolation tools" chapter

- added feature information to the "Troubleshooting charts" chapter

- added "Troubleshooting an StrAlc alarm" section to the "Advanced troubleshooting procedures" chapter

- deleted "Responding to mismatch logs" section in "Advanced troubleshooting procedures" chapter

#### August 1995

CSP04 Standard 05.02

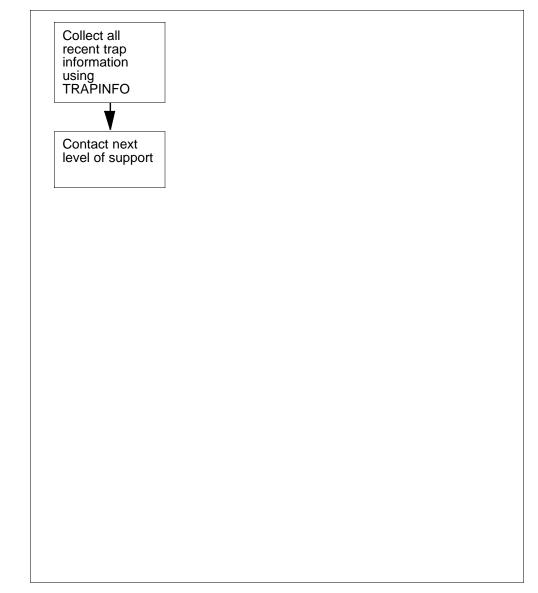

Added "Responding to a CMTrap alarm procedure" to "Advanced troubleshooting procedures" chapter

#### May 1995

CSP04 Standard 05.01

- added feature information to the "Overview" chapter

- added feature information to the "Preventive maintenance strategies" chapter

- added feature information to the "Logs" chapter

- added feature information to the "User interface and commands" chapter

- added feature information to the "Cards and paddle boards" chapter

- added feature information to the "Trouble isolation tools" chapter

- added feature information to the "Troubleshooting charts" chapter

- added feature information to the "Advanced troubleshooting procedures" chapter

## January 1995

CSP03 Preliminary 04.01

- added feature information to the "Preventive maintenance strategies" chapter

- added feature information to the "Logs" chapter

- added feature information to the "Troubleshooting charts" chapter

- added feature information to the "Advanced troubleshooting procedures" chapter

#### April 1994

CSP02 Preliminary 03.01

CSP02 is a temporary identification that identifies a preliminary release of post-BCS36 NTPs.

• added feature information to the "Logs" chapter

## December 1993

BCS36 Standard 02.02

• incorporated editor and technical review changes

# September 1993

BCS36 Preliminary 02.01

Added the following chapters:

- "Trouble isolation tools"

- "Troubleshooting charts"

- "Advanced troubleshooting procedures"

Added information to the chapters that remain based on design review and feature updates.

## March 1993

BCS35 Preliminary 01.01 first release of document

# Contents

| Ab | out this document<br>How to check the version and issue of this document xiii<br>References in this document xiii | xii  |

|----|-------------------------------------------------------------------------------------------------------------------|------|

| 1  | Overview                                                                                                          | 1-1  |

|    | DMS SuperNode and SuperNode SE system architecture 1-1<br>DMS SuperNode and SuperNode SE cabinet layouts 1-3      |      |

|    | DMS SuperNode and SuperNode SE computing module architecture<br>Processor and memory 1-6<br>Interfaces 1-8        | 1-5  |

|    | Reset control 1-10                                                                                                |      |

|    | Bus termination 1-11<br>Bus extension 1-11                                                                        |      |

|    | Subsystem clock 1-11                                                                                              |      |

|    | Power supply 1-11                                                                                                 |      |

|    | DMS SuperNode and SuperNode SE computing module configuration                                                     | 1-11 |

| 2  | Preventive maintenance strategies                                                                                 | 2-1  |

|    | Routine maintenance procedures 2-1                                                                                |      |

|    | Automatic maintenance 2-2                                                                                         |      |

|    | Mismatch handler 2-2                                                                                              |      |

|    | Software audits 2-3<br>Routine exercise tests 2-3                                                                 |      |

|    | Indications of automatic test results 2-10                                                                        |      |

| 3  | Logs                                                                                                              | 3-1  |

|    | DMS SuperNode and SuperNode SE CM-related logs 3-1                                                                |      |

|    | Computing module logs 3-1                                                                                         |      |

|    | Footprint logs 3-9                                                                                                |      |

|    | Input/output audit logs 3-10<br>Mismatch logs 3-10                                                                |      |

| 4  | Operational measurements                                                                                          | 4-1  |

| -  | DMS SuperNode and SuperNode SE CM-related OMs 4-1                                                                 |      |

|    | Computing module group 4-1                                                                                        |      |

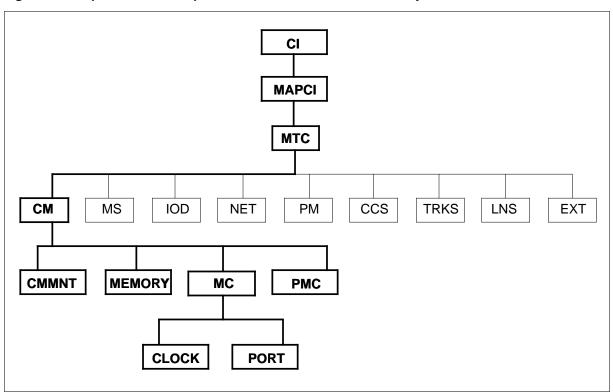

| 5  | User interface and commands                                                                                       | 5-1  |

|    | DMS SuperNode and SuperNode SE CM subsystem commands 5-1                                                          |      |

```

CM level unlisted menu commands 5-2

SRAMCNT commands 5-3

CM level status field indicators 5-4

CMMNT level unlisted menu commands 5-5

CMMNT level status filed indicators 5-6

Memory level unlisted menu commands 5-7

Memory level status field indicators 5-8

MC level unlisted menu commands 5-9

MC level status field indicators 5-10

Port level unlisted menu commands 5-10

Port level status field indicators 5-11

Clock level unlisted menu commands 5-11

Clock level status field indicators 5-12

PMC level unlisted menu commands 5-13

PMC level status field indications 5-14

Reset terminal commands 5-14

5-14

Series 50Mx SuperNode and Series 70 SuperNode and SuperNode SE

commands 5-20

QRYMEM 5-20

Usage examples 5-20

Error messages 5-21

SYNC 5-25

Usage examples 5-26

Error messages 5-27

CONFIG 5-27

Usage examples 5-28

TST 5-28

Usage examples 5-29

TRNSL 5-29

Usage examples 5-30

CNTRS 5-31

Usage examples 5-31

LOCATE 5-32

Usage examples 5-32

Error messages 5-32

MATCH 5-33

Usage examples 5-33

Error messages 5-34

MMINFO 5-35

Usage examples 5-36

Warning messages for the MMINFO command 5-38

Error messages 5-39

CM mismatch commands 5-41

SYNC 5-41

Error messages 5-43

SWAPHW 5-45

Usage examples 5-46

Warning messages 5-47

Error messages 5-49

UNSWAPHW 5-50

```

6-1

Usage examples 5-51 Warning messages 5-51 Error messages 5-52 CLRALARM 5-52 Usage examples 5-53 Error messages 5-54 MMINFO 5-54 Usage examples 5-55 MMSYNC 5-55 Usage examples 5-57

## Cards and paddle boards DMS SuperNode and SuperNode SE CM card and paddle board descriptions 6-1 NT9X10 BRISC CPU card 6-3 NT9X12 CPU port card 6-9 NT9X13 CPU card 6-10 NT9X14 memory card 6-12 NT9X20 DS512 interface paddle board 6-14 NT9X21 bus terminator paddle board 6-15 NT9X22 subsystem clock paddle board 6-15 NT9X26 reset terminal interface paddle board 6-15 NT9X27 bus extender paddle board 6-17 NT9X30 +5V power converter card 6-18 NT9X31 -5V power converter 6-18 NT9X46 parallel port interface paddle board 6-19 NT9X62 SR512 paddle board 6-19 NT9X86 dual-port message controller card 6-19 NTDX15 power converter card 6-20

## 7 Trouble isolation tools

6

Diagnostic tools 7-1 Alarms 7-1 DMSMON 7-3 Log reports 7-3 MTCTST 7-3 Maintenance manager's morning report 7-4 MMINFO 7-4 OM-log-alarm cross-reference charts 7-5 Operational measurements 7-5 Sherlock 7-5 Switch performance monitoring system 7-5 TRAPINFO 7-6

# 8 Troubleshooting charts

CM alarm and trouble condition procedures 8-1 OM-log-alarm cross reference charts 8-6 Memory limits and alarms 8-14 Memory alarm cross reference charts 8-14 LowMem alarm 8-15

#### 8-1

7-1

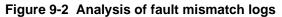

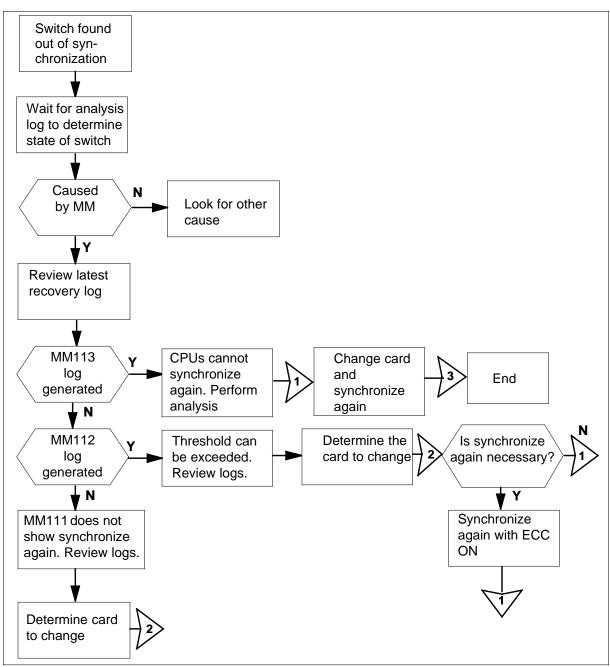

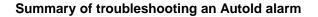

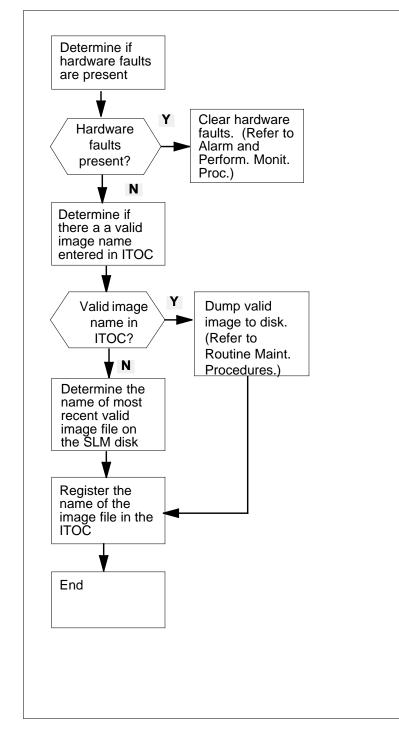

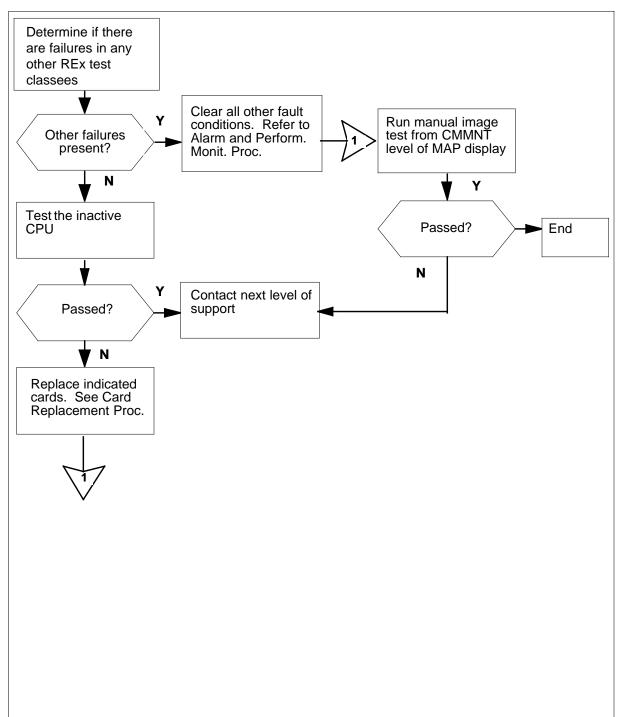

StrAlc alarm 8-16 LOWSpr and LowSpr alarms 8-18 MemLim alarm 8-19 SLMLIM and SLMLim alarms 8-19 9 9-1 **Mismatch analysis** Mismatch system response 9-1 Mismatch handler 9-2 General mismatch thresholds 9-2 Mismatch alarms 9-2 Mismatch logs 9-4 Mismatch fault log 9-4 Mismatch recovery log 9-4 Mismatch tools 9-5 MMINFO 9-5 MMSYNC command 9-5 General analysis of mismatch logs 9-6 Mismatch analysis 9-7 Fault mismatch logs 9-8 Single bit memory fault correctable mismatches 9-11 Interpretation of mismatch logs 9-14 M68K/88K mismatch fault conditions 9-14 BRISC M88K mismatch log 9-25 Memory fault correctable mismatch log 9-28 10 10-1 Advanced troubleshooting procedures Task list 10-1 Responding to a CMTrap alarm 10-2 Responding to a PrcOpt alarm 10-7 Troubleshooting a RExFlt alarm 10-9 Troubleshooting a RExSch alarm 10-11 Troubleshooting an Autold alarm 10-13 Troubleshooting an IMAGE critical alarm 10-15 Troubleshooting an StrAlc alarm 10-17

# List of terms

A-1

# About this document

This document helps maintenance personnel locate and clear faults in the computing module. This document applies to the DMS SuperNode and the DMS SuperNode SE switches.

# How to check the version and issue of this document

This document uses numbers (like 01.01) to indicate the version and issue of the document.

The first two digits indicate the version. The version number increases with each update that support a new software release. For example, the first release of a document is 01.01. In the *next* software release cycle, the first release of the same document is 02.01.

The second two digits indicate the issue. The issue number increases with each revision when the document is released again in the *same* software release cycle. For example, the second release of a document in the same software release cycle is 01.02.

Determine which version of this document applies to the software you have and determine the order of this document. Refer to the release information in *Product Documentation Directory*.

# **References in this document**

This document refers to the following documents:

- Switch Performance Monitoring System Application Guide, 297-1001-330

- DMS-100 Family Commands Reference Manual, 297-1001-822

- DMS SuperNode and SuperNode SE Message Switch Maintenance Guide, 297-5001-549

- Alarm and Performance Monitoring Procedures

- Card Replacement Procedures

- Log Report Reference Manual

- Operational Measurements Reference Manual

- Routine Maintenance Procedures

- Trouble Locating and Clearing Procedures

# 1 Overview

This chapter provides an overview of the DMS SuperNode (SN) and DMS SuperNode SE (SNSE) switches and the architecture of the computing module (CM).

This chapter consists of the following sections:

Section, "DMS SuperNode and SuperNode SE system architecture" on page 1-1 describes SuperNode and SuperNode SE system architecture.

Section, "DMS SuperNode and SuperNode SE cabinet layouts" on page 1-3 illustrates the SuperNode and SuperNode SE cabinet layouts.

Section, "DMS SuperNode and SuperNode SE computing module architecture" on page 1-5 describes SuperNode and SuperNode SE CM architecture.

Section, "DMS SuperNode and SuperNode SE computing module configuration" on page 1-11 describes SuperNode and SuperNode SE CM configurations.

# DMS SuperNode and SuperNode SE system architecture

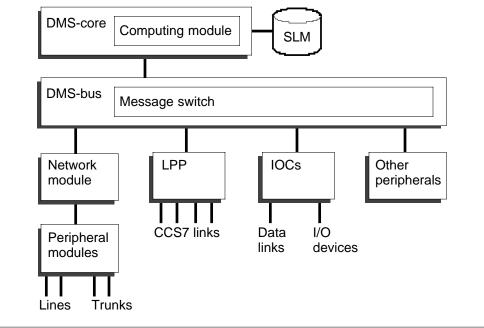

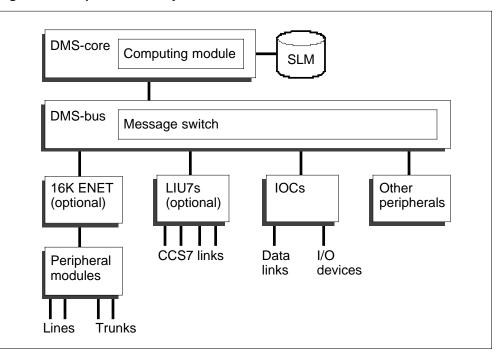

The SN and SNSE systems, in Figure 1-1, "SuperNode system architecture" on page 1-2 and Figure 1-2, "SuperNode SE system architecture" on page 1-3, share the following components:

- DMS-core

- DMS-bus

- DMS-link

The DMS-core provides data storage and computing resources. The DMS-core contains a duplexed CM and two system load modules (SLM).

The DMS-bus processes and distributes messages to nodes in the SuperNode and SNSE switches. The DMS-bus contains two message switches (MS) that share loads.

The DMS-link allows the DMS-core and DMS-bus to communicate with each other. The DMS also allows the DMS-core and the DMS-bus to communicate with other nodes in the SN and SNSE switches.

The user can configure the SNSE with a 16K enhanced network (ENET) and CCS7 link interface units (LIU7). The 16K ENET provides voice and data signal switching for nodes in the SNSE switch. The 16K ENET also provides message routes to the MS. The LIU7 provides CCS7 message processing.

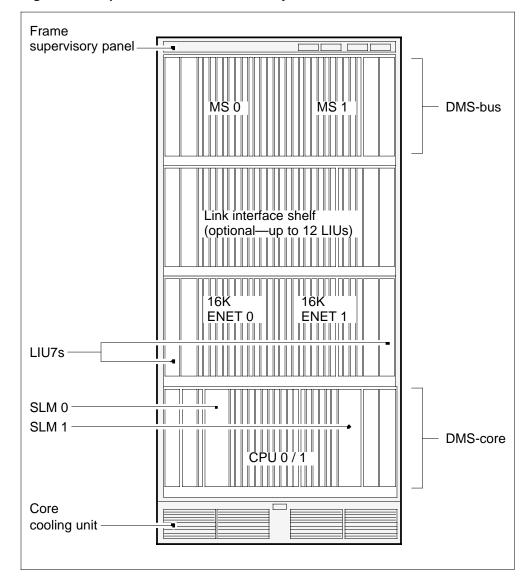

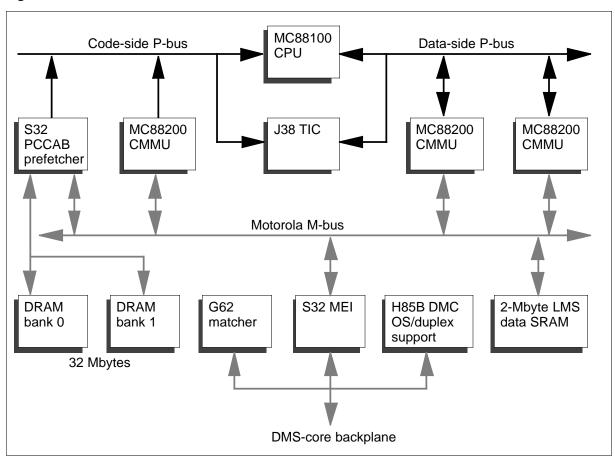

Figure 1-1 SuperNode system architecture

Figure 1-2 SuperNode SE system architecture

# DMS SuperNode and SuperNode SE cabinet layouts

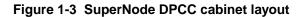

In a SN cabinet, the CM does not share a shelf. In a SNSE cabinet, the CM shares a shelf with the SLMs. The SN cabinet is called the dual plane combined core (DPCC) cabinet. The SNSE cabinet is called the SN combined core (SCC) cabinet. Figure 1-3, "SuperNode DPCC cabinet layout" on page 1-4 and Figure 1-4, "SuperNode SE SCC cabinet layout" on page 1-5 show SN and SNSE cabinet layouts.

## 1-4 Overview

Figure 1-4 SuperNode SE SCC cabinet layout

# DMS SuperNode and SuperNode SE computing module architecture

The CM architecture is the same in the SN and SNSE switches. The CM contains the following subsystems:

- processor and memory

- interfaces

- reset control

- bus termination

- bus extension

- subsystem clock

- power supply

For redundancy, the CM contains two identical planes. Each plane can carry the full processing load. During normal synchronized operation, one plane is active and controls call processing activity. The system updates the inactive plane with the active plane. The inactive plane can control call processing activity if a problem occurs on the active plane.

#### **Processor and memory**

The processor and memory system consists of CPU cards (NT9X10 or NT9X13) and memory cards (NT9X14). The processor and memory system controls call processing and configuration and maintenance of the other systems.

The NT9X10 and NT9X13 CPU cards house microprocessor circuits and a limited amount of memory for program store. The NT9X14 memory cards provide additional memory for data store.

Burst mode provides fast memory access. When burst mode is active, each fetch operation reads four words of data. Fetch operations normally read one word.

The SN switch uses the following CPU card and memory card groups:

- NT9X13BB and NT9X14DB

- NT9X13BC and NT9X14BB

- NT9X13BC and NT9X14DB

- NT9X13GA and NT9X14BB

- NT9X13GA and NT9X14DB

- NT9X13HB and NT9X14BB

- NT9X13HB and NT9X14DB

- NT9X10AA and NT9X14DB

- NT9X10AA and NT9X14EA

- NT9X10BA and NT9X14EA

- NT9X10CA and NT9X14EA

- NT9X10DA and NT9X14FA

The SNSE switch uses the following CPU card and memory card groups:

- NT9X13MA and NT9X14DB

- NT9X13MB and NT9X14EA

- NT9X13MB and NT9X14DB

- NT9X10AA and NT9X14EA

- NT9X10BA and NT9X14EA

- NT9X10BA and NT9X14EA

- NT9X10CA and NT9X14EA

- NT9X10DA and NT9X14FA

# Modes of operation

The SN and SNSE switches use two processors with matched synchronization. These processors are designed for duplex operation. When the switch operates normally, the processors are synchronized. The synchronization provides protection from faults.

The processors can run out of synchronization or in split mode (split) for different maintenance operations. A description of these three modes of operation follows.

# In sync

Both CPUs perform call processing when the CM runs in synchronisation. The memory contents of the two planes are the same. The active CPU has write control over all message controller (MC) ports. The inactive CPU can read from all MC ports, but does not have write access.

If a hardware fault causes the two CPUs to be out of synchronization, matcher circuitry on the processor cards flag a mismatch. The mismatch handler must determine which side is sane (fault free). The mismatch handler makes sure the CPU that does not have faults is active. The mismatch handler also makes sure that synchronization drops.

# Out of sync

When the CM runs while out of synchronization, the system isolates the inactive CPU from call processing activity. The active CPU initiates firmware processes on the CPU that is not active. The active CPU performs this action to test the hardware on the plane that is not active.

The system uses out of synchronization mode to perform maintenance on the inactive plane. The maintenance system can initiate this mode when the system detects a fault. Maintenance personnel can also begin the mode manually.

# Split

When the CM runs in split mode, both CPUs run on their own. The CPUs use one or two the links to communicate to each other. For call processing, one CPU operates as active and does all call processing. The system uses split mode while software is upgraded. When a switch is split, the operating company personnel can load software to the inactive plane. The data tables on the active plane can copy on to the inactive plane over the split links. When the process is complete, personnel can perform a controlled switch of activity to activate the CPU that is not active.

## Interfaces

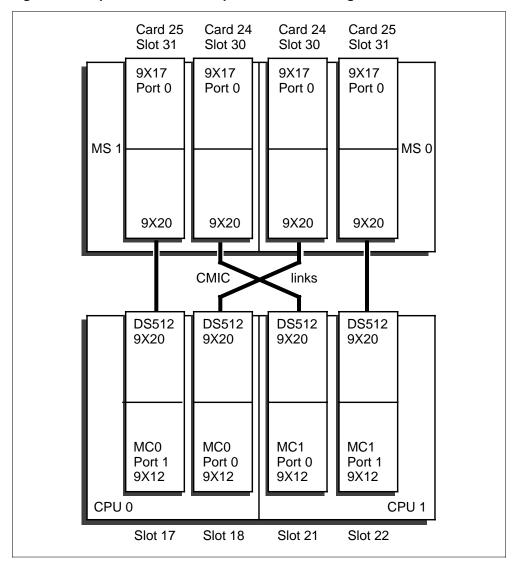

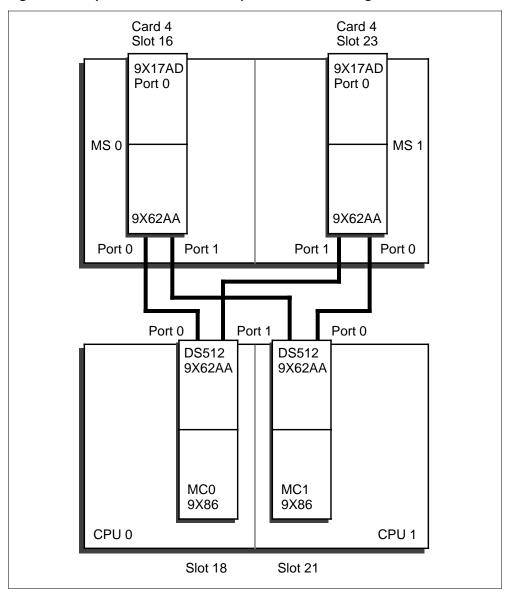

In-band communication between the CM and the MSs occurs through port cards, interface paddle boards and DS512 fiber optic cables. The SN uses two NT9X12 single-port cards and two NT9X20 DS 512 paddle boards on each CM plane. One card and paddle board pair connects to each MS. The SNSE uses one NT9X86 dual-port card and one NT9X62 interface paddle board on each CM plane.

Communication between each CM plane and the corresponding SLM occurs with one NT9X12 single-port card and one NT9X46 interface paddle board. For SN, the card and paddle board are in the SLM shelf. The bus extension connects the card and paddle to the CM plane. For SNSE, the card and paddle board reside within the CM part of the CM/SLM shelf.

Port cards and paddle boards group into functional blocks. The peripheral module controller (PMC) is the name for the logical grouping of ports that communicate with the SLMs and the bus extenders.

The message controller is the name for the logical grouping of ports on each CM plane that communicates with both MSs. The complete messaging path between the CM and MSs consists of the following components:

- MCs (one on each CM plane)

- computing module interface cards (CMIC) (two on each MS)

- DS512 cables (CMIC links)

Figure 1-5, "SuperNode CM-to-MS port connection diagram" on page 1-9 and Figure 1-6, "SuperNode SE CM-to-MS port connection diagram" on page 1-10 show the port connections for SuperNode and SuperNode SE CM-to-MS communication.

Figure 1-5 SuperNode CM-to-MS port connection diagram

Figure 1-6 SuperNode SE CM-to-MS port connection diagram

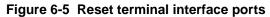

## **Reset control**

Processor state information appears on the reset terminal. The reset terminal provides a utility for local and remote resetting of the CM. The NT9X26 RTIF paddle board has two interface ports. One port connects to the local reset terminal and the other port connects to an optional remote reset terminal.

When the subsystem functions normally, the reset system is in a monitoring mode. A CPU can require initialization to a known state for maintenance, bootloading or error recovery. If this event occurs the reset system initiates the reset sequence to initialize the processor.

# **Bus termination**

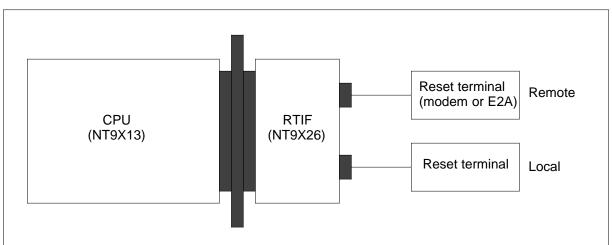

The NT9X21 paddle board provides resistive termination for the A32 system bus in the CM.

# **Bus extension**

The NT9X27 CM bus extension paddle board links the CM and the SLM shelf.

# Subsystem clock

Each SN CM plane contains a subsystem clock (SSC) paddle board (NT9X22) that provides link synchronization with the MS. The SNSE subsystem clock circuits are integrated on the NT9X62 interface paddle board. The office clock in the MS determines SSC accuracy for the SN and SNSE subsystem clock circuits.

Time-of-day (TOD) clocking circuits are on the SuperNode NT9X12 port cards and on the SuperNode SE NT9X86 dual port cards. The office clock in the MS determines TOD accuracy.

# **Power supply**

The power supply provides power for the CM processor shelf. The SN power supply has two +5V dc power converters (NT9X30) and two -5V dc power converters (NT9X31). On SNSE, two 5V dc power converters (NTDX15) power the CM part of the shelf.

# DMS SuperNode and SuperNode SE computing module configuration

Figure 1-7, "Example of a Series 20 to 40 SuperNode computing module shelf layout" on page 1-12 and Figure 1-8, "Example of a Series 20 to 40 SuperNode SE CM/SLM shelf layout" on page 1-13 show example Series 20 to 60 SN and SNSE CM shelf layouts.

Figure 1-9, "Example of a Series 50 to 70 SuperNode CM/SLM shelf layout" on page 1-14 and Figure 1-10, "Example of a Series 50 to 70 SuperNode SE CM/SLM shelf layout" on page 1-15 show example Series 70 SN and SNSE CM shelf layouts.

#### 1-12 Overview

|   |     |             |                    | NT9X3 | 0 +5V 86-A power converter | 36F |

|---|-----|-------------|--------------------|-------|----------------------------|-----|

| _ |     |             |                    | NT9X3 | 1 -5V 20-A power converter | 33F |

| 3 | 32R | NT9X21      | CM-bus terminator  | NT9X1 | 4 Memory                   | 32F |

| 3 | 31R | NT9X27A     | ACM-bus extender   | NT9X1 | 4 Memory                   | 31F |

| 3 | BOR | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 30F |

| 2 | 29R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 29F |

| 2 | 28R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 28F |

| 2 | 27R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 27F |

| 2 | 26R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 26F |

| 2 | 25R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 25F |

| 2 | 24R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 24F |

| 2 | 23R | NT9X22      | CM subsystem clock | NT9X1 | 4 Memory                   | 23F |

| 2 | 22R | NT9X20      | DS512              | NT9X1 | 2 CPU port                 | 22F |

|   | 21R | NT9X20      | DS512              | NT9X1 | 2 CPU port                 | 21F |

| 2 | 20R | NT9X26      | RTIF               | NT9X1 | 3 CPU                      | 20F |

| 1 | 19R | NT9X26      | RTIF               | NT9X1 | 3 CPU                      | 19F |

| 1 | 18R | NT9X20      | DS512              | NT9X1 | 2 CPU port                 | 18F |

| 1 | 17R | NT9X20      | DS512              | NT9X1 | 2 CPU port                 | 17F |

| 1 | 16R | NT9X22      | CM subsystem clock | NT9X1 | 4 Memory                   | 16F |

| 1 | 15R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 15F |

| 1 | 14R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 14F |

| 1 | 13R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 13F |

| 1 | 12R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 12F |

| 1 | 11R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 11F |

| 1 | 10R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 10F |

| 0 | )9R | NT9X19      | Filler faceplate   | NT9X1 | 4 Memory                   | 09F |

| 0 | 08R | NT9X27A     | ACM-bus extender   | NT9X1 | 4 Memory                   | 08F |

|   | )7R | NT9X21      | CM-bus terminator  | NT9X1 | 4 Memory                   | 07F |

| L |     | Paddle b    | oards              | 1     |                            |     |

|   |     |             |                    | NT9X3 | 0 +5V 86-A power converter | 04F |

|   |     | : Use fille |                    | NT9X3 | 1 -5V 20-A power converter | 01F |

| Figure 1-7 Example of a Series 20 to 40 SuperNode computing module shelf layout |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

|      |     |                              |                                   | 1         | 1     |

|------|-----|------------------------------|-----------------------------------|-----------|-------|

|      |     |                              | NT9X91AA +12/+5V power converter  | 36F       |       |

|      |     |                              | NTDX15AA +5/-5V power converter   | 33F       |       |

|      | 32R | NT9X19BAFiller               |                                   | İ         |       |

|      | 31R | NT9X19BAFiller               |                                   |           |       |

|      | 30R | NT9X19BAFiller               |                                   |           |       |

|      | 29R | NT9X19BAFiller               |                                   |           |       |

|      | 28R | NT9X46AAParallel CM port I/F | NT9X44AC System load module 1A    | 28F       |       |

| Rear | 27R | NT9X21ABCM bus terminator    | NT9X14EA Memory                   | 27F       |       |

|      | 26R | NT9X19BAFiller               | NT9X14EA Memory                   | 26F       |       |

|      | 25R | NT9X19BAFiller               | NT9X14EA Memory                   | 25F       |       |

|      | 24R | NT9X19BAFiller               | NT9X14EA Memory                   | 24F       |       |

|      | 23R | NT9X19BAFiller               | NT9X14EA Memory                   | 23F       |       |

|      | 22R | NT9X46AAParallel CM port I/F | NT9X12AC Single-port message card | 22F       |       |

|      | 21R | NT9X62AADual-link SR512 I/F  | NT9X86AA Dual-port message card   | 21F       | Front |

|      | 20R | NT9X26ABRTIF                 | NT9X13MB CPU                      | 20F       | ц     |

|      | 19R | NT9X26ABRTIF                 | NT9X13MB CPU                      | 19F       |       |

|      | 18R | NT9X62AADual-link SR512 I/F  | NT9X86AA Dual-port message card   | 18F       |       |

|      | 17R | NT9X46AAParallel CM port I/F | NT9X12AC Single-port message card | <br>  17F |       |

|      | 16R | NT9X19BAFiller               | NT9X14EA Memory                   | 16F       |       |

|      | 15R | NT9X19BAFiller               | NT9X14EA Memory                   | 15F       |       |

|      | 14R | NT9X19BAFiller               | NT9X14EA Memory                   | 14F       |       |

|      | 13R | NT9X19BAFiller               | NT9X14EA Memory                   | 13F       |       |

|      | 12R | NT9X21ABCM bus terminator    | NT9X14EA Memory                   | <br>  12F |       |

|      | 11R | NT9X19BAFiller               |                                   | i         |       |

|      | 10R | NT9X19BAFiller               |                                   |           |       |

|      | 09R | NT9X19BAFiller               |                                   |           |       |

|      | 08R | NT9X19BAFiller               |                                   |           |       |

|      | 07R | NT9X46AAParallel CM port I/F | NT9X44AC System load module 1A    | 07F       |       |

|      | L   | Paddle boards                |                                   | İ         |       |

|      |     |                              | NTDX15AA +5/-5V power converter   | 04F       |       |

|      |     |                              | NT9X91AA +12/+5V power converter  | 01F       |       |

|      |     |                              | Cards                             |           | -     |

Figure 1-8 Example of a Series 20 to 40 SuperNode SE CM/SLM shelf layout

## 1-14 Overview

|     | Paddleboa   | ards                  |                |                          | Cards |

|-----|-------------|-----------------------|----------------|--------------------------|-------|

|     |             |                       | NT9X30         | +5V 86-A power converter | 36F   |

|     |             |                       | NT9X30         | -5V 20-A power converter | 33F   |

| 32R | NT9X21      | CM-bus terminator     | NT9X14         | Memory                   |       |

| 31R | NT9X27AA    | CM-bus extender       | NT9X14         | Memory                   | 31F   |

| 30R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 30F   |

| 29R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 29F   |

| 28R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 28F   |

| 27R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 27F   |

| 26R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 26F   |

| 25R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 25F   |

| 24R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 24F   |

| 23R | NT9X22      | CM subsystem clock    | NT9X14         | Memory                   | 23F   |

| 22R | NT9X20      | DS512                 | NT9X12         | CPU port                 | 22F   |

| 21R | NT9X20      | DS512                 | NT9X12         | CPU port                 | 21F   |

| 20R | NT9X26      | RTIF                  | NT9X10         | CPU                      | 20F   |

| 19R | NT9X26      | RTIF                  | NT9X10         | CPU                      | 19F   |

| 18R | NT9X20      | DS512                 | NT9X12         | CPU port                 | 18F   |

| 17R | NT9X20      | DS512                 | NT9X12         | CPU port                 | 17F   |

| 16R | NT9X22      | CM subsystem clock    | NT9X14         | Memory                   | 16F   |

| 15R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 15F   |

| 14R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 14F   |

| 13R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 13F   |

| 12R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 12F   |

| 11R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 11F   |

| 10R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 10F   |

| 09R | NT9X19      | Filler faceplate      | NT9X14         | Memory                   | 09F   |

| 08R | NT9X27AA    | CM-bus extender       | NT9X14         | Memory                   | 08F   |

| 07R | NT9X21      | CM-bus terminator     | NT9X14         | Memory                   | 07F   |

|     |             |                       | NT9X30         | +5V 86-A power converter | 04F   |

|     |             |                       | NT9X30         | -5V 20-A power converter | 01F   |

| <   | Rear        |                       |                |                          | Front |

|     | Note: Loc f | iller faceplate (NT9X | 10) to fill or | ntv elote                | ·     |

|     | 1010. 036 1 |                       |                |                          |       |

## Figure 1-9 Example of a Series 50 to 70 SuperNode CM/SLM shelf layout

|      |     |                              | NT9X91AA+12/+5V power converter  | 36F              |  |

|------|-----|------------------------------|----------------------------------|------------------|--|

|      | Г   |                              | NTDX15AA+5/-5V power converter   | 33F              |  |

|      | 32R | NT9X19 Filler faceplate      |                                  |                  |  |

|      | 31R | NT9X19 Filler faceplate      |                                  |                  |  |

|      | 30R | NT9X19 Filler faceplate      |                                  |                  |  |

|      | 29R | NT9X19 Filler faceplate      |                                  |                  |  |

|      | 28R | NT9X46AAParallel CM port I/F | NT9X44ACSystem load module 1A    | 28F              |  |

|      | 27R | NT9X21ABCM bus terminator    | NT9X14EAMemory                   | 27F              |  |

| Rear | 26R | NT9X19 Filler faceplate      | NT9X14EAMemory                   | 26F              |  |

|      | 25R | NT9X19 Filler faceplate      | NT9X14EAMemory                   | 25F              |  |

|      | 24R | NT9X19 Filler faceplate      | NT9X14EAMemory                   | 24F              |  |

|      | 23R | NT9X19 Filler faceplate      | NT9X14EAMemory                   | 23F              |  |

|      | 22R | NT9X46AAParallel CM port I/F | NT9X12ACSingle-port message card | 22F              |  |

|      | 21R | NT9X62AADual-link SR512 I/F  | NT9X86AADual-port message card   |                  |  |

|      | 20R | NT9X26EARTIF                 | NT9X10ABCPU                      | 20F <sup>正</sup> |  |

|      | 19R | NT9X26EARTIF                 | NT9X10ABCPU                      | 19F              |  |

|      | 18R | NT9X62AADual-link SR512 I/F  | NT9X86AADual-port message card   | 18F              |  |

|      | 17R | NT9X46AAParallel CM port I/F | NT9X12ACSingle-port message card | 17F              |  |

|      | 16R | NT9X19 Filler faceplate      | NT9X14EAMemory                   |                  |  |

|      | 15R | NT9X19 Filler faceplate      | NT9X14EAMemory                   | 15F              |  |

|      | 14R | NT9X19 Filler faceplate      | NT9X14EAMemory                   | 14F              |  |

|      | 13R | NT9X19 Filler faceplate      | NT9X14EAMemory                   | 13F              |  |

|      | 12R | NT9X21ABCM bus terminator    | NT9X14EAMemory                   | 12F              |  |

|      | 11R | NT9X19 Filler faceplate      |                                  |                  |  |

|      | 10R | NT9X19 Filler faceplate      |                                  |                  |  |

|      | 09R | NT9X19 Filler faceplate      |                                  |                  |  |

|      | 08R | NT9X19 Filler faceplate      |                                  |                  |  |

|      | 07R | NT9X46AAParallel CM port I/F | NT9X44 System load module 1A     | 07F              |  |

|      |     | Paddle boards                |                                  |                  |  |

|      |     |                              | NTDX15 +5/-5V power converter    | 04F              |  |

|      |     |                              | NT9X91 +12/+5V power converter   | 01F              |  |

|      |     |                              | Cards                            |                  |  |

Figure 1-10 Example of a Series 50 to 70 SuperNode SE CM/SLM shelf layout

# **2** Preventive maintenance strategies

This chapter lists the preventive routine maintenance procedures that operating company personnel must perform. This chapter describes the automatic maintenance activities that the DMS SuperNode (SN) and the DMS SuperNode SE (SNSE) computing module (CM) perform.

This chapter consists of the sections that follow:

#### **Routine maintenance procedures**

page 2-1 lists the preventive maintenance procedures that apply to the SN and SNSE.

#### Automatic maintenance

page 2-2 describes the system-run processes that detect, repair and report problems.

# **Routine maintenance procedures**

Operating company personnel perform routine procedures according to a schedule. Routine procedures keep the hardware and software of the switch fault-free. Some of the following procedures do not directly relate to the CM. These procedures do affect switch operations.

The CM preventive procedures contain the following:

- cleaning system load module (SLM) tape drive heads

- verifying and adjust the time-of-day (TOD) clock

- testing wrist-strap grounding cords

- replacing cooling unit filters

- testing power converter voltages.

For instructions on how to perform these procedures, see *Routine Maintenance Procedures*.

# Automatic maintenance

The primary source for error detection in the CM is the mismatch handler. The CM also runs software audits and routine exercise (REx) tests to detect faults.

# **Mismatch handler**

The mismatch handler for Series 20 to 60 SN is a software program that can determine which call pickup (CPU) is at fault. Differences in operation can occur between the two planes of the CM.

The mate exchange bus (MEB) monitors data that the CPUs send and receive. When the data that the CPUs send and receive does not match, both CPUs raise a mismatch interrupt. When a mismatch occurs, the mismatch handler tests each CPU and determines the correct CPU.

The following events occur during a mismatch:

- system drops synchronization

- system queries the hardware for faults

- system synchronizes CPUs again

- system copies data for in-synchronization analysis

- system runs matcher test to make sure that the CM remains synchronized

- system analyzes hardware fault indication register (FIR)

- system analyzes memory

- system analyzes address hold register (AHR)

- system compares microprocessor status registers

- system compares microprocessor address and data registers

The process terminates when the system finds a fault. The mismatch logs contain the information from the queries and analysis. Progress markers and error messages in the log reports indicate where the fault is in the sequence. The mismatch handler can end the analysis cycle before the handler isolates a fault. When the mismatch handler cannot isolate the fault, the analysis result indicates that a transient fault caused the mismatch.

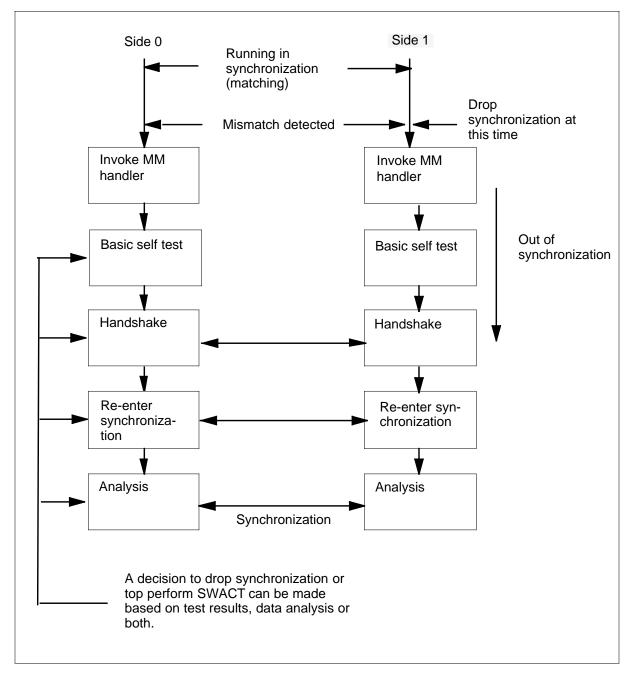

For Series 70 SuperNode, the mismatch handler performs the mismatch analysis and diagnostics in duplex is not in synchronization mode. In this mode, both CPUs perform mismatch handling when coupled to the mate CPU. This coupling involves handling and data exchange between the CPUs and controlled activity switching, to allow diagnostics to proceed safely. With this out-of-synchronization approach, both CPUs are ready to take activity. Both CPUs can proceed with the normal operation if the other side fails to meet. The SR70 mismatch handler handles faults by priority. The handler does not handle faults in the order they are found.

#### Software audits

Software audits are the scheduled programs that the CPU runs to monitor the state of CM.

#### Computing module duplex audit

The CM duplex audit runs every 5 s to determine the status of the CM. The audit updates the user interface when the status changes. The audit resets the mismatch thresholds each hour.

The audit determines the state of the CPU and the E2A links, and the jam status. To determine these states, the audit queries the processor card or reads the correct reset terminal interface (RTIF) register. The audit compares the current status with the status determined the last time the audit ran. When necessary, the audit updates the user interface information.

When a Switch of Activity (SWACT) occurs, the system records a footprint entry. The system transfers system logs and footprint buffers, if the system failed to complete the transfer after the last restart or no-restart SWACT.

#### Subsystem clock/time-of-day clock audit

The subsystem audits the subsystem clocks (SSC) once each minute. The subsystem audits the TOD clocks in 2 min intervals to make sure the clocks function normally.

#### Computing module link audit

A link audit tests the computing module interface card (CMIC) links each minute to make sure the CMIC links function normally.

#### Message switch link audit

The message switch (MS) requests that the CM test the CMIC links in 5 min intervals to make sure CMIC links function normally.

#### **Routine exercise tests**

The CM routine exercise (REX) tests are preventive maintenance procedures that identify latent hardware failures. REX tests allow the correction of the faults before an outage or performance degradation occurs. The system schedules CM REX tests for automatic execution. Operating company personnel can request manual CM REX tests at the CM level of the MAP. When the system performs a REX test, a REX test indication appears under the CM header of the MTC level MAP display.

*Note:* Perform a manual maintenance test (MTCTST) to detect faults on new hardware installations or hardware that may have faults. For more

information about MTCTST, refer to Chapter 7, "Trouble isolation tools" on page -1 in this document.

## **Base CM REX test**

The base CM REX test includes the following test activities:

- 1. pre-REX stability check

- 2. pre-REX inventory check

- 3. CM image test

- 4. Switch of activity (SWACT)

## Full CM REX test

The full CM REX test includes the following test activities:

- 1. pre-REX stability check

- 2. pre-REX inventory check

- 3. CM image test

- 4. out-of-synchronization tests that are not destructive

- 5. out-of-synchronization destructive tests

- 6. in-synchronization tests that are not destructive

- 7. SWACT

- 8. in-synchronization tests that are not destructive

- 9. out-of-synchronization destructive tests

- 10. 0out-of-synchronization tests that are not destructive.

The scheduled REX tests generated by the system run each night at the default time of 1:30 a.m. On Wednesdays, the system runs the full REX test. On all other days of the week, the system runs the base REX test. The user can modify this schedule through datafill. Refer to procedure "Changing CM REX intensity" in *Routine Maintenance Procedures*.

Before the system begins an REX test, the system checks the dedicated stability threshold counters. These counters monitor static random access memory (SRAM) parity fault counts. If these counters record a large number of SRAM parity faults in a period before the test request, the system responds as follows:

• If operating company personnel generate the REX test request manually, a warning and confirmation prompt appear on the MAP. These prompts

indicate that the REX test is not advised. Personnel can choose to abort or execute the test.

• When the REX test is scheduled for automatic execution, the system aborts the test and generates an alarm and a log. The alarm and log indicate the reason that the test did not proceed.

The stability of the system is monitored during execution of REX tests. If a mismatch, trap, link closure, or restart occur during a REX test, the system aborts the remainder of the test. The system resets the CM to a known state.

## **REX test results reporting**

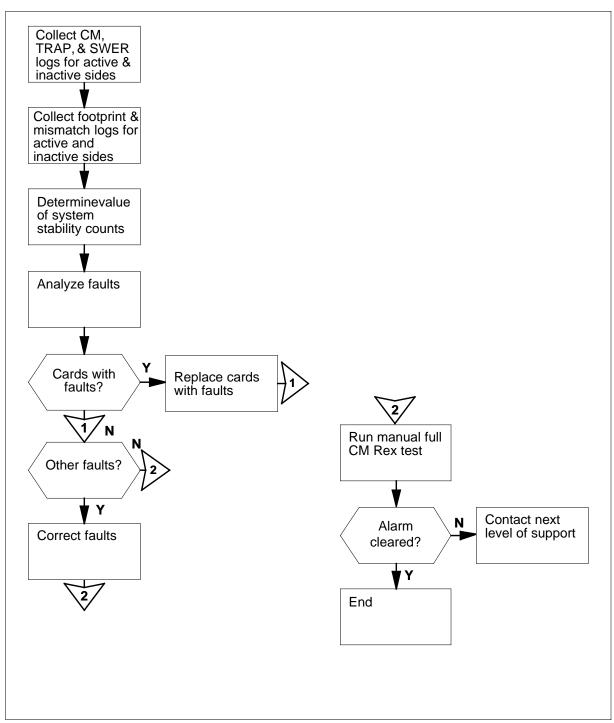

When the system performs a CM REX test, the system produces a CM179 log that indicates if the test passes or fails. If the test fails, the system raises a CM Flt major alarm. The CM179 log indicates the reason for the test failure, the class of the failed test and a list of suspect hardware.

If REX test generated by the system cannot complete because of switch conditions, the system produces a failure reason message. The following conditions prevent the completion of the system REX test:

- The mate is jammed inactive. A complete REX test includes a switch of activity between the active processors and the processors that are not active. A jam condition prevents a SWACT.

- The mate CPU is under test. Another maintenance activity is in process, and the REX test cannot interfere.

- The CPUs are not synchronized. A complete REX test includes dropping of synchronization and synchronizing again. To perform this action, the CPUs must synchronize at the beginning.

- System resources are not available. The system cannot allocate enough resources to run the REX test. The REX tests must run at low traffic periods.

To clear the alarm when a CM REX test fails, run the test again on the failed CPU.

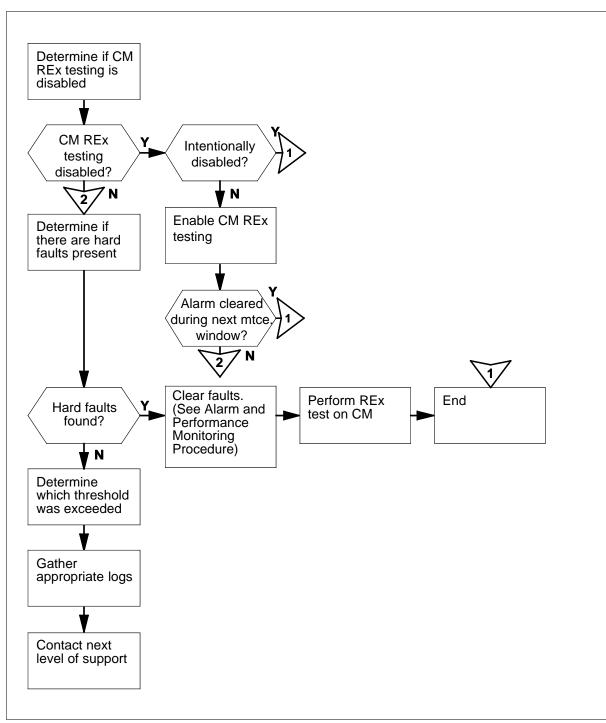

If the REX test cannot start because of error conditions that exceed preset thresholds, a REXSch alarm appears. The alarm appears under the CM header of the MTC level MAP display. The alarm clears when the system completes a manual REX. For the instructions to clear this alarm, refer to Chapter 10, "Advanced troubleshooting procedures" on page -1. Refer also to *Alarm and Performance Monitoring Procedures*.

## **CPU class REX tests**

The following table lists the tests in the CPU class REX test for the MC68000 NT9X13 family of processors.

| Table 2-1 | CPU class REX tests | (NT9X13 processors) |

|-----------|---------------------|---------------------|

|-----------|---------------------|---------------------|

| Test name                | Description                                                                                                                                                                                                                                                                        |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| inact_mau_rex            | Executes firmware self-test on the inactive CPU for the memory access unit (MAU). This test checks MAU address decodes, parity detection, access protection mask bits, range error detection, latching of all error status bits, and latching of appropriate FIR bits on an error. |

| inact_clock_rex          | Makes sure the circuit of the inactive CPU can detect clock failures.                                                                                                                                                                                                              |

| inact_rtif_rex           | Exercises the remote terminal interface (RTIF) diagnostics of the inactive CPU.                                                                                                                                                                                                    |

| inact_reset_rex          | Checks the ability of the inactive CPU to handle manual and mate resets.                                                                                                                                                                                                           |

| inact_interrupt_rex      | Checks the ability of the inactive CPU to handle different types of interrupts. This test does not check level 1 interrupts. The link class of REX tests checks level 1 interrupts.                                                                                                |

| inact_access_prot_rex    | Makes sure the access protection RAM of the inactive CPU can contain access protection mapping.                                                                                                                                                                                    |

| inact_os_timer_rex       | Tests the operating system timer circuit on the inactive CPU.                                                                                                                                                                                                                      |

| inact_address_hold_rex   | Makes sure the address hold register can latch an address. The test runs in firmware.                                                                                                                                                                                              |

| inact_interrupt_mask_rex | Makes sure all bits of the interrupt mask register can be set.                                                                                                                                                                                                                     |

| inact_data_cache_rex     | Tests the data cache memory and control of the inactive CPU. This test includes a:                                                                                                                                                                                                 |

|                          | march over cache RAM                                                                                                                                                                                                                                                               |

|                          | a check of cache parity and parity RAM                                                                                                                                                                                                                                             |

|                          | a check for proper cache hit and miss.                                                                                                                                                                                                                                             |

| inact_mate_fir_rex       | Makes sure that all bits on the FIR of the inactive CPU that can be<br>set. Bits remain on the FIR so that the active CPU can determine if<br>its mate FIR can read the latched status.                                                                                            |

| inact_rom_checksum_rex   | Makes sure that the ROM is not corrupt on the inactive CPU.                                                                                                                                                                                                                        |

| Test name        | Description                                                                                                                                                                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| inact_sanity_rex | Forces the inactive CPU through a complete sanity breakdown. This test does not write to the primary or the super-sanity timer. When the first timer expires, the system generates an interrupt. When the second timer expires, a reset occurs. This test checks these events and the time between these events. |

| matcher_rex      | Makes sure mismatch detection circuits work. The system runs this test under firmware control and when the CPUs are in synchronization.                                                                                                                                                                          |

#### Table 2-1 CPU class REX tests (NT9X13 processors)

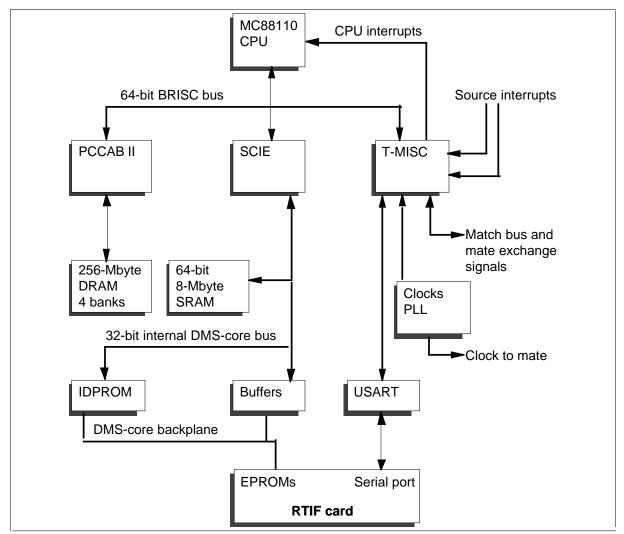

The following table lists the tests in the CPU class REX test for the MC88100 BRISC NT9X10AA family of processors.

| Test name                | Description                                                                                          |

|--------------------------|------------------------------------------------------------------------------------------------------|

| inact_clock_rex          | Makes sure that the inactive CPU clock circuit can detect clock failures.                            |

| inact_rtif_rex           | Exercises the RTIF diagnostics of the inactive CPU.                                                  |

| inact_reset_rex          | Checks the ability of the inactive CPU to handle manual and mate resets.                             |

| mate_fir_rex             | Tests that the FIR latches and that the active CPU can read the FIR through the mate FIR.            |

| inact_rom_checksum_rex   | Makes sure that the ROM is not corrupt on the inactive CPU.                                          |

| inact_tic_rex_timer      | Tests tracer/interrupt controller (TIC) timing functions.                                            |

| inact_tic_rex_config     | Tests TIC basic functions.                                                                           |

| inact_tic_rex_interrupt  | Tests the ability of the TIC to generate and mask interrupts.                                        |

| inact_tic_rex_trace      | Tests the tracing functions of the TIC.                                                              |

| inact_mei_parity_rex     | Tests the ability of the memory bus (M-bus) Ecore interface (MEI) to detect and latch parity errors. |

| inact_mei_mem_access_rex | Tests the ability of MEI to detect and latch invalid memory accesses.                                |

| inact_mei_rto_rex        | Tests the ability of MEI to detect and latch response time-out errors.                               |

| inact_pccab_rex          | Tests the prefetcher with circular content addressable buffer (PCCAB) functions.                     |

| Test name        | Description                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| inact_sanity_rex | Forces the inactive CPU through a sanity breakdown. This test does<br>not write to the primary or the super-sanity timer. When the first timer<br>expires, the system generates an interrupt. When the second timer<br>expires, a reset occurs. This test checks these events and the time<br>between these events. |

| matcher_rex      | Tests matching on the processor bus (P-Bus) and ECore backplane.                                                                                                                                                                                                                                                    |

#### Table 2-2 CPU class REX tests (NT9X10AA BRISC processors)

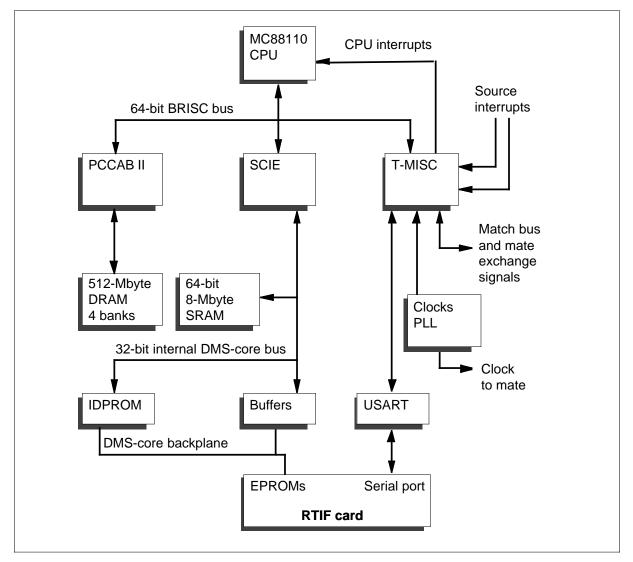

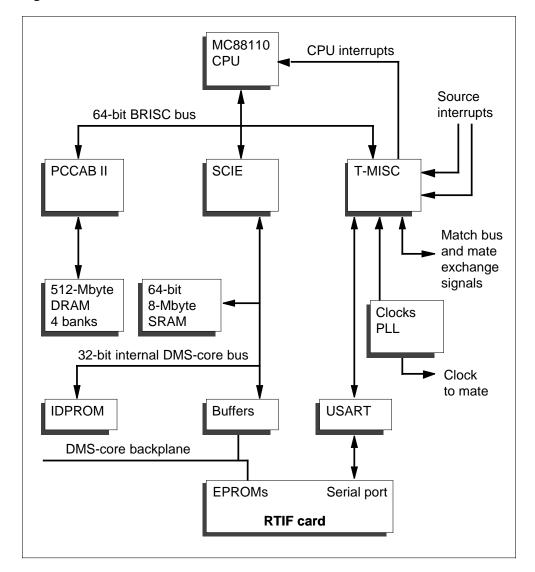

The following table lists the tests in the CPU class REX test for the MC88110 BRISC NT9X10BA, NT9X10CA and NT9X10DA group of processors:

| Test name                 | Description                                                                                                                                                                                                                                                                                                         |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| inact_reset_rex           | Checks the ability of the inactive CPU to handle manual and mate resets.                                                                                                                                                                                                                                            |

| inact_sanity_rex          | Forces the inactive CPU through a sanity breakdown. This test does<br>not write to the primary or the super-sanity timer. When the first timer<br>expires, the system generates an interrupt. When the second timer<br>expires, a reset occurs. This test checks these events and the time<br>between these events. |

| mate_fir_rex              | Tests that the FIR latches and that the active CPU can read the FIR through the mate FIR.                                                                                                                                                                                                                           |

| matcher_rex               | Tests the BRISC Bus matching.                                                                                                                                                                                                                                                                                       |

| inact_rom_checksum_rex    | Makes sure the ROM is not corrupt on the inactive CPU.                                                                                                                                                                                                                                                              |

| inact_rtif_rex            | Exercises the RTIF diagnostics of the inactive CPU.                                                                                                                                                                                                                                                                 |

| inact_mei_mem_access_rex  | Tests the ability of SCIE to detect and latch invalid memory accesses.                                                                                                                                                                                                                                              |

| inact_mei_rto_rex         | Tests the ability of SCIE to detect and latch response time-out errors.                                                                                                                                                                                                                                             |

| inact_tic_rex_interrupt   | Tests the ability of the TMISC to generate and mask interrupts.                                                                                                                                                                                                                                                     |

| inact_pc2_ecc_enabled_rex | Invokes F/W test pccab2_ecc_enabled_RAM test.                                                                                                                                                                                                                                                                       |

| inact_pc2_march_dlw_rex   | Invokes F/W test pccab2_march_dlw_test.                                                                                                                                                                                                                                                                             |

| inact_pll_rex             | Invokes F/W out of frequency PLL test.                                                                                                                                                                                                                                                                              |

## Table 2-3 CPU class REX tests (NT9X10BA/NT9X10CA BRISC processors)

| Test name                           | Description                                 |

|-------------------------------------|---------------------------------------------|

| inact_lms_march_ecc_enabl<br>ed_rex | Invokes F/W test Ims_march_test_ecc_enabled |

| inact_tmisc_tracer_rex              | Invokes F/W TMISC tracer test.              |

#### Table 2-3 CPU class REX tests (NT9X10BA/NT9X10CA BRISC processors)

## Memory routine exercise tests

The following table lists the memory class tests:

#### Table 2-4 Memory class REX tests (all CM processors)

| Test name             | Description                                                                                             |

|-----------------------|---------------------------------------------------------------------------------------------------------|

| inact_mem_control_rex | Performs a firmware memory module controller test for each memory module on the inactive CPU.           |

| inact_mem_decode_rex  | Programs the mate addressing configuration and checks for double decodes between memory modules.        |

| inact_mem_march_rex   | Performs a destructive march test for the memory cards at the rate of one card for each CPU each night. |

#### Link routine exercise tests

The link class REX test checks the operation of the message controller (MC). The MC consists of ports, SSCs and TOD clocks. The MC runs if all links are in-service. The link class tests appear in the following table.

#### Table 2-5 Link class REX tests (all CPU processors)

| Test name             | Description                                                                                                                                                                       |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mc_split_mode_rex     | Places the CM in split mode. Batch change supplement (BCS) applications require split mode. If the system cannot place the CM in split mode, the test fails.                      |

| mc_inservice_test_rex | Performs an in-service test on the MC.                                                                                                                                            |

| mc_port_test_rex      | Takes the MC links that do not have faults out of service one at a time, and performs destructive tests on the MC links. The tests include all hardware and error modes provided. |

| mc_test_rex           | Takes a complete MC out of service and performs a destructive MC test on the MC.                                                                                                  |

| ssc0_rex_general_test | Performs a REX test on the SSC.                                                                                                                                                   |

| Test name             | Description                         |

|-----------------------|-------------------------------------|

| ssc1_rex_general_test | Performs a REX test on the SSC.     |

| ssc_id_prom_test_rex  | Reads the IDProms of the SSC cards. |

#### Table 2-5 Link class REX tests (all CPU processors)

#### Peripheral module controller routine exercise tests

The peripheral module controller (PMC) class REX tests are like the link class tests. The system performs these tests when all links are in service. The PMC class tests appear in the following table.

Table 2-6 PMC class REX tests (all CM processors)

| Test name         | Description                                      |

|-------------------|--------------------------------------------------|

| pmc_port_test_rex | Tests the PMC port and link handler hardware.    |

| pmc_node_test_rex | Tests the PMC with the crossover bus of the PMC. |

## **Base class routine exercise tests**

The base class tests appear in the following table.

#### Table 2-7 Base class REX tests (all CM processors)

| Test name                  | Description                                                                                  |

|----------------------------|----------------------------------------------------------------------------------------------|

| inact_rex_image_test       | Tests inactive image to make sure the image can start again.                                 |

|                            | Tests restart capabilities on a rotational basis in a three night cycle:                     |

|                            | tests warm restart capabilities on the first night                                           |

|                            | tests cold restart capability the second nightt                                              |

|                            | <ul> <li>tests reload restart capabilities the third night. The rotation repeats.</li> </ul> |

| cm_rex_check_inventor<br>y | Makes sure all product equipment codes (PECs) meet baseline requirements.                    |

#### Indications of automatic test results

The following indicators inform operating company personnel of the results of automatic maintenance tests:

- alarms

- logs

- operational measurements (OMs).

To detect and resolve minor problems, operating company personnel must monitor these indicators for trends and patterns.

For information on how to clear alarms, refer to Chapter 8, "Troubleshooting charts" on page -1, and *Alarm and Performance Monitoring Procedures*. For more information about logs, refer to Chapter 3, "Logs" on page -1, and the *Log Report Reference Manual*. For more information about the OMs, refer to Chapter 4, "Operational measurements" on page -1, and the *Operational Measurements Reference Manual*.

## 2-12 Preventive maintenance strategies

# 3 Logs

This chapter describes logs that relate to the DMS SuperNode and DMS SuperNode SE computing module (CM).

Logs provide information to monitor the components of the CM. Some logs can isolate a problem to one component. Other logs can indicate problems that cannot be attributed to one component.

# DMS SuperNode and SuperNode SE CM-related logs

The following types of logs relate to CMs:

- computing module (CM)

- footprint (FP)

- input/output audit (IOAU)

- mismatch (MM)

Chapter 10, "Advanced troubleshooting procedures" on page -1 provides information used to analyze the root cause of the most difficult logs. For more detailed information on logs, refer to the Log Report Reference Manual.

## **Computing module logs**

The logs report information from the following:

- CPU

- CM cards

- subsystem clocks (SSC)

- imaging

- traps

- routine exercise (REX) tests

- link tests

# Table 3-1 lists the SN and SNSE CM logs and triggers.

| Log   | Title                        | Trigger                                                                                                                                                                                                                                                 |

|-------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CM100 | SUMM CM REPORT               | The system generates this summary report each day at 9:00 a.m. This log provides the status of the CM.                                                                                                                                                  |

| CM101 | INFO CM STATUS               | A change in the CM synchronized, activity, jam status, or CPU clock source.                                                                                                                                                                             |

| CM102 | INFO CM STATUS               | The system generates this log one time each hour when the CM is out of synchronization.                                                                                                                                                                 |

| CM103 | TBL HIGH TRAP RATE           | The occurrence of many traps. The log specifies the number of traps that occur each minute.                                                                                                                                                             |

| CM104 | SYSB MC STATUS<br>CHANGE     | A change in state of the message controller indicates system busy (SysB). The log report indicates the reason for the state change.                                                                                                                     |