# **Critical Release Notice**

Publication number: 297-8991-805 Publication release: Standard 11.03

# The content of this customer NTP supports the SN06 (DMS) software release.

Bookmarks used in this NTP highlight the changes between the LEC0015 baseline and the current release. The bookmarks provided are color-coded to identify release-specific content changes. NTP volumes that do not contain bookmarks indicate that the LEC0015 baseline remains unchanged and is valid for the current release.

#### **Bookmark Color Legend**

Black: Applies to new or modified content for LEC0015 that is valid through the current release.

**Red:** Applies to new or modified content for SN04 (DMS) that is valid through the current release.

Blue: Applies to new or modified content for SN05 (DMS) that is valid through the current release.

Green: Applies to new or modified content for SN06 (DMS) that is valid through the current release.

*Attention! Adobe*® *Acrobat*® *Reader*™ 5.0 or higher is required to view bookmarks in color.

## **Publication History**

#### June 2005

Standard release 11.03 for software release SN06 (DMS). Updates made for this release are shown below:

#### Volume 5

Added NTDX16AA (Q00946403)

#### March 2004

Standard release 11.02 for software release SN06 (DMS). Updates made for this release are shown below:

#### Volumes 1 – 3

No changes

#### Volume 4

Card NT9X30AB is Manufacture Discontinued and is replaced by new card NT9X30AC.

#### Volume 5

No changes

#### September 2003

Standard release 11.01 for software release SN06 (DMS). Updates made for this release are shown below:

#### <u>Volumes 1 – 4</u>

No changes

#### Volume 5

Updates were made to NT9X76AA according to CR Q00177945.

## 297-8991-805

## DMS-100 Family Hardware Description Manual Volume 4 of 5

2001Q1 Standard 09.01 March 2001

## DMS-100 Family Hardware Description Manual

Volume 4 of 5

Publication number: 297-8991-805 Product release: 2001Q1 Document release: Standard 09.01 Date: March 2001

Copyright © 1994-2001 Nortel Networks, All Rights Reserved

Printed in the United States of America

**NORTEL NETWORKS CONFIDENTIAL:** The information contained herein is the property of Nortel Networks and is strictly confidential. Except as expressly authorized in writing by Nortel Networks, the holder shall keep all information contained herein confidential, shall disclose the information only to its employees with a need to know, and shall protect the information, in whole or in part, from disclosure and dissemination to third parties with the same degree of care it uses to protect its own confidential information, but with no less than reasonable care. Except as expressly authorized in writing by Nortel Networks, the holder is granted no rights to use the information contained herein.

Information is subject to change without notice. Nortel Networks reserves the right to make changes in design or components as progress in engineering and manufacturing may warrant. Changes or modifications to the DMS-100 without the express consent of Nortel Networks may void its warranty and void the user's authority to operate the equipment.

Nortel Networks, the Nortel Networks logo, the Globemark, How the World Shares Ideas, Unified Networks, DMS, DMS-100, Helmsman, MAP, Meridian, Nortel, Northern Telecom, NT, and SuperNode are trademarks of Nortel Networks..

## Contents

## Volume 4 of 5

| 1 | NT6Xnnaa (c | ontinued)                              |     |

|---|-------------|----------------------------------------|-----|

|   | NT6X69DA th | rough NT6X99AA (continued from Vol. 3) | 1-1 |

|   | NT6X69DA 1  | 1-2                                    |     |

|   | NT6X69LA 1  | -9                                     |     |

|   | NT6X69LB 1  | -17                                    |     |

|   | NT6X69MA    | 1-25                                   |     |

|   | NT6X69QA    | 1-33                                   |     |

|   | NT6X70AA 1  | 1-38                                   |     |

|   | NT6X70CA    | 1-42                                   |     |

|   | NT6X71AA 1  | 1-46                                   |     |

|   | NT6X71AB 1  | 1-52                                   |     |

|   | NT6X71AC    | 1-58                                   |     |

|   | NT6X71BA 1  | 1-62                                   |     |

|   | NT6X72AA 1  | 1-67                                   |     |

|   | NT6X72BA 1  | 1-71                                   |     |

|   | NT6X73AA 1  | 1-75                                   |     |

|   | NT6X73BA 1  | 1-77                                   |     |

|   | NT6X75AA 1  | 1-79                                   |     |

|   | NT6X75DA    | 1-87                                   |     |

|   | NT6X75EA 1  | 1-95                                   |     |

|   | NT6X75KA 1  | 1-103                                  |     |

|   | NT6X76AA 1  | 1-111                                  |     |

|   | NT6X76AC    | 1-117                                  |     |

|   | NT6X76AD    | 1-121                                  |     |

|   | NT6X78AA 1  | 1-126                                  |     |

|   | NT6X78AB 1  | 1-132                                  |     |

|   | NT6X78BA 1  | 1-137                                  |     |

|   | NT6X79AA 1  | 1-150                                  |     |

|   | NT6X79AB 1  | 1-153                                  |     |

|   |             | 1-156                                  |     |

|   |             | 1-164                                  |     |

|   |             | 1-171                                  |     |

|   |             | 1-180                                  |     |

|   |             | 1-187                                  |     |

|   |             | 1-194                                  |     |

|   |             | 1-200                                  |     |

|   |             | 1-203                                  |     |

1-1

|   | NT6X92BC 1-209<br>NT6X92CA 1-217<br>NT6X92EA 1-223<br>NT6X93AA 1-232<br>NT6X93BA 1-236<br>NT6X93CA 1-240<br>NT6X93CA 1-240<br>NT6X93DA 1-245<br>NT6X93EA 1-249<br>NT6X93FA 1-253<br>NT6X95AB 1-256<br>NT6X99AA 1-260 |                                       |     |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|

| 2 | NT7Xnnaa                                                                                                                                                                                                             |                                       | 2-1 |

|   | NT7X03AA through NT7X90AA                                                                                                                                                                                            | 2-1                                   |     |

|   | NT7X03AA 2-2                                                                                                                                                                                                         |                                       |     |

|   | NT7X07AA 2-5                                                                                                                                                                                                         |                                       |     |

|   | NT7X26AE 2-20                                                                                                                                                                                                        |                                       |     |

|   | NT7X38AB 2-24                                                                                                                                                                                                        |                                       |     |

|   | NT7X53AA 2-26                                                                                                                                                                                                        |                                       |     |

|   | NT7X76BA 2-29                                                                                                                                                                                                        |                                       |     |

|   | NT7X80AA 2-31                                                                                                                                                                                                        |                                       |     |

|   | NT7X90AA 2-33                                                                                                                                                                                                        |                                       |     |

| 3 | NT8Xnnaa                                                                                                                                                                                                             |                                       | 3-1 |

|   | NT8X01AA through NT8X49AB                                                                                                                                                                                            | 3-1                                   |     |

|   | NT8X01AA 3-2                                                                                                                                                                                                         |                                       |     |

|   | NT8X01BB 3-8                                                                                                                                                                                                         |                                       |     |

|   | NT8X02AB 3-15                                                                                                                                                                                                        |                                       |     |

|   | NT8X04AA 3-19                                                                                                                                                                                                        |                                       |     |

|   | NT8X04BA 3-23                                                                                                                                                                                                        |                                       |     |

|   | NT8X05AA 3-27                                                                                                                                                                                                        |                                       |     |

|   | NT8X06AB 3-29                                                                                                                                                                                                        |                                       |     |

|   | NT8X06BA 3-31                                                                                                                                                                                                        |                                       |     |

|   | NT8X10AA 3-33                                                                                                                                                                                                        |                                       |     |

|   | NT8X11AB 3-36                                                                                                                                                                                                        |                                       |     |

|   | NT8X13AA 3-44                                                                                                                                                                                                        |                                       |     |

|   | NT8X18BA 3-49                                                                                                                                                                                                        |                                       |     |

|   | NT8X40AA 3-57                                                                                                                                                                                                        |                                       |     |

|   | NT8X48AD 3-63                                                                                                                                                                                                        |                                       |     |

|   | NT8X49AB 3-73                                                                                                                                                                                                        |                                       |     |

| 4 | NT9Xnnaa                                                                                                                                                                                                             |                                       | 4-1 |

| - | NT9X01BA through NT9X74BA                                                                                                                                                                                            | (continued in Volume 5) 4-1           |     |

|   | •                                                                                                                                                                                                                    | · · · · · · · · · · · · · · · · · · · |     |

|   | NT9X01BA 4-2                                                                                                                                                                                                         |                                       |     |

|   |                                                                                                                                                                                                                      |                                       |     |

|   | NT9X01DA 4-6                                                                                                                                                                                                         |                                       |     |

|   | NT9X01DA 4-6<br>NT9X01JA 4-10                                                                                                                                                                                        |                                       |     |

|   | NT9X01DA 4-6<br>NT9X01JA 4-10<br>NT9X01JB 4-14                                                                                                                                                                       |                                       |     |

|   | NT9X01DA 4-6<br>NT9X01JA 4-10                                                                                                                                                                                        |                                       |     |

| NT9X04AB | 4-33         |

|----------|--------------|

| NT9X04AE | 4-39         |

| NT9X04AH | 4-45         |

| NT9X05AB | 4-53         |

| NT9X05AC | 4-56         |

| NT9X05AD | 4-50<br>4-59 |

|          | 4-59<br>4-62 |

| NT9X06AA |              |

| NT9X06AB | 4-66         |

| NT9X06AC | 4-70         |

| NT9X06AD | 4-74         |

| NT9X06AF | 4-78         |

| NT9X07CA | 4-80         |

| NT9X10AA | 4-84         |

| NT9X10DA | 4-96         |

| NT9X12AB | 4-104        |

| NT9X12AC | 4-110        |

| NT9X12AD | 4-116        |

| NT9X13BB | 4-124        |

| NT9X13BC | 4-128        |

| NT9X13CA | 4-132        |

| NT9X13DA | 4-138        |

| NT9X13DB | 4-142        |

| NT9X13DC | 4-146        |

| NT9X13DD | 4-150        |

| NT9X13DE | 4-156        |

| NT9X13FA | 4-162        |

| NT9X13GA | 4-166        |

| NT9X13UA | 4-173        |

| NT9X13HB | 4-173        |

| NT9X13HB | 4-187        |

| NT9X13LA | 4-107        |

|          |              |

| NT9X13MA | 4-199        |

| NT9X13MB | 4-205        |

| NT9X14AA | 4-211        |

| NT9X14BB | 4-215        |

| NT9X14DB | 4-219        |

| NT9X14EA | 4-223        |

| NT9X14FA | 4-232        |

| NT9X15AA | 4-241        |

| NT9X17AA | 4-246        |

| NT9X17AC | 4-253        |

| NT9X17AD | 4-261        |

| NT9X17BB | 4-267        |

| NT9X17CA | 4-274        |

| NT9X17DA | 4-282        |

| NT9X20AA | 4-288        |

| NT9X20BB | 4-293        |

| NT9X20BC | 4-298        |

| NT9X21AA | 4-304        |

| NT9X21AB | 4-308        |

| NT9X22CA | 4-312        |

|          | 1012         |

|          | 1 217 |

|----------|-------|

|          | 4-317 |

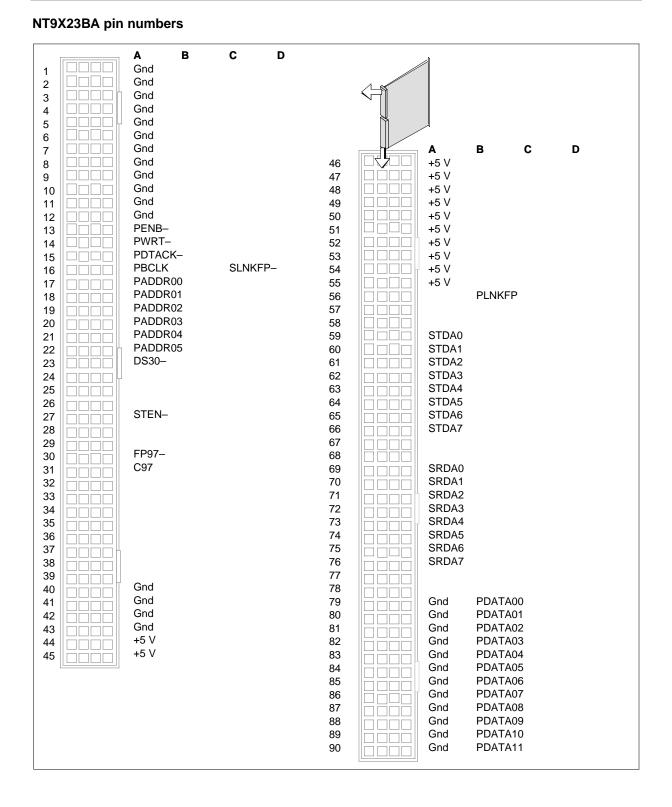

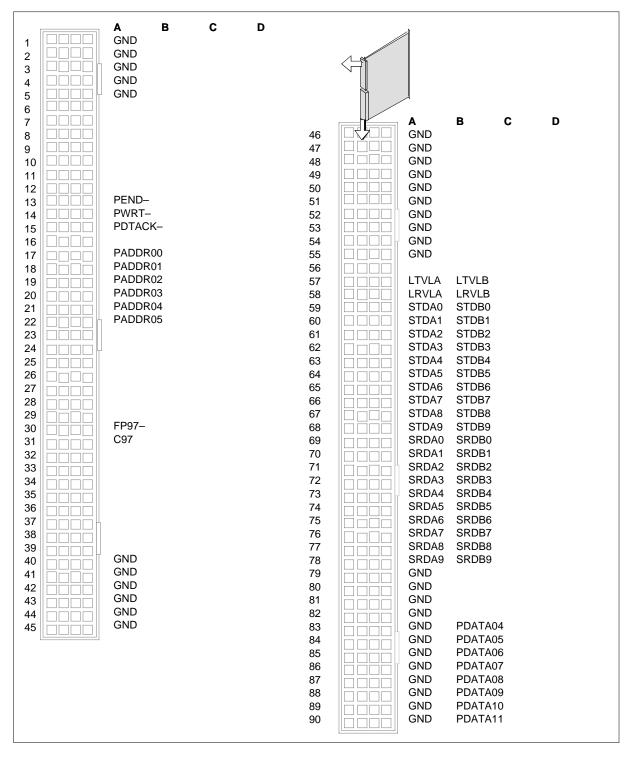

| NT9X23BA | 4-322 |

| NT9X25AA | 4-326 |

| NT9X25BA | 4-330 |

| NT9X26AA | 4-334 |

| NT9X26AB |       |

|          | 4-338 |

| NT9X26DA | 4-342 |

| NT9X26DB | 4-348 |

| NT9X26DC | 4-354 |

| NT9X26GA | 4-361 |

| NT9X27AA | 4-369 |

| NT9X27BA | 4-373 |

|          |       |

| NT9X30AA | 4-377 |

| NT9X30AC | 4-380 |

| NT9X31AA | 4-385 |

| NT9X31AB | 4-388 |

| NT9X32AA | 4-393 |

| NT9X35CA | 4-395 |

|          |       |

| NT9X35FA | 4-401 |

| NT9X36BA | 4-407 |

| NT9X40BA | 4-414 |

| NT9X40BB | 4-418 |

| NT9X41BA | 4-422 |

| NT9X44AB | 4-433 |

|          |       |

| NT9X44AC | 4-441 |

| NT9X44AD | 4-449 |

| NT9X45BA | 4-458 |

| NT9X46AA | 4-466 |

| NT9X47AA | 4-476 |

| NT9X47AB | 4-480 |

| NT9X49BA | 4-486 |

|          |       |

| NT9X49CA | 4-489 |

| NT9X49CB | 4-494 |

| NT9X49CC | 4-498 |

| NT9X52AA | 4-504 |

| NT9X53AA | 4-511 |

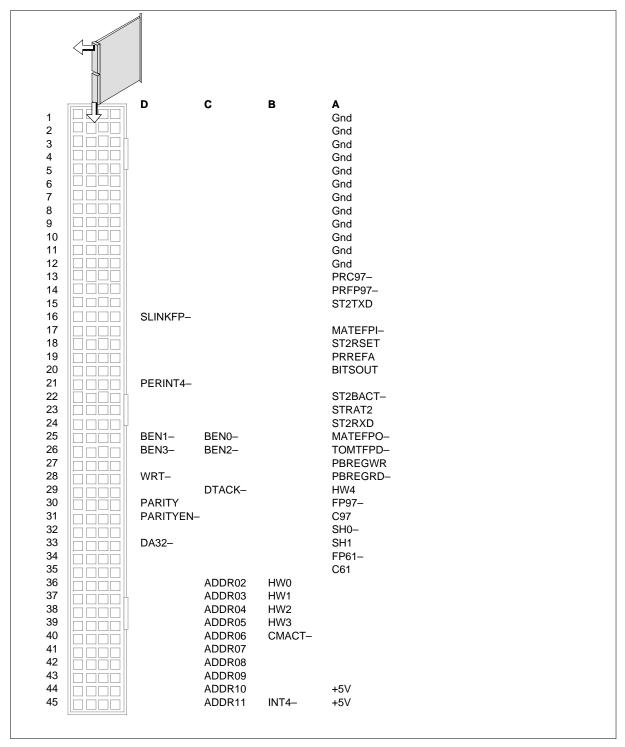

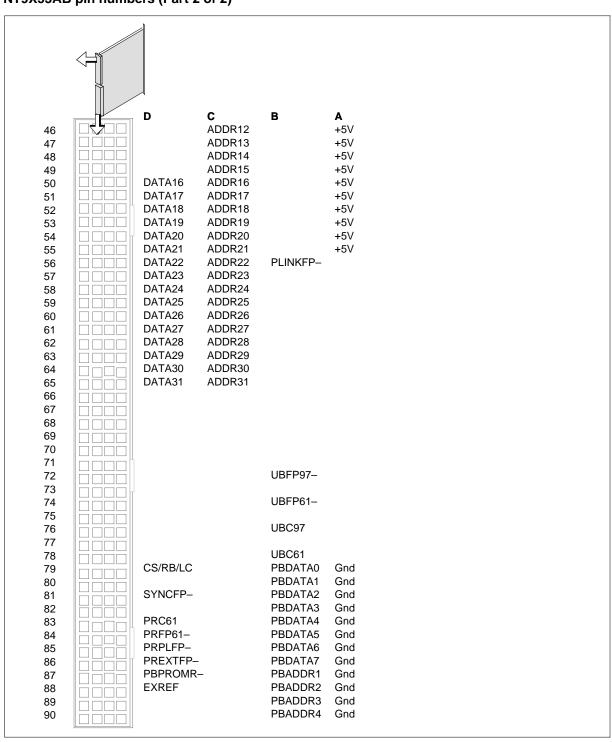

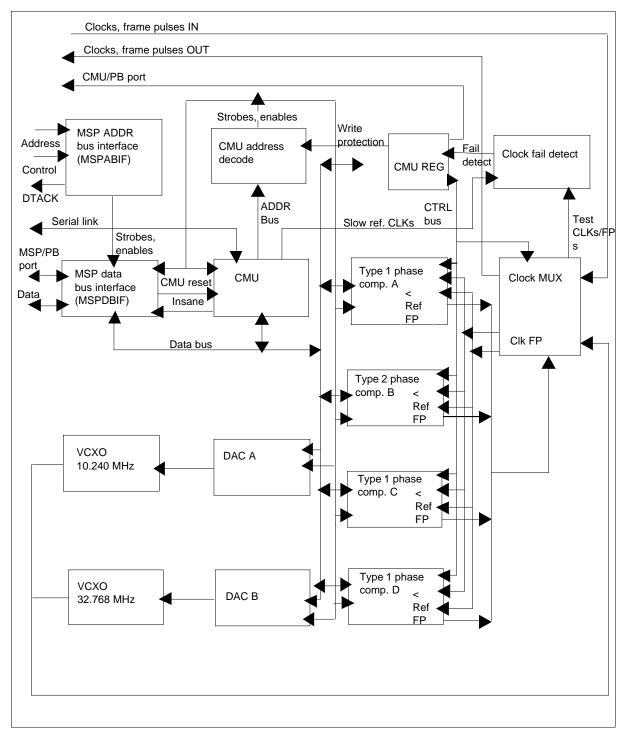

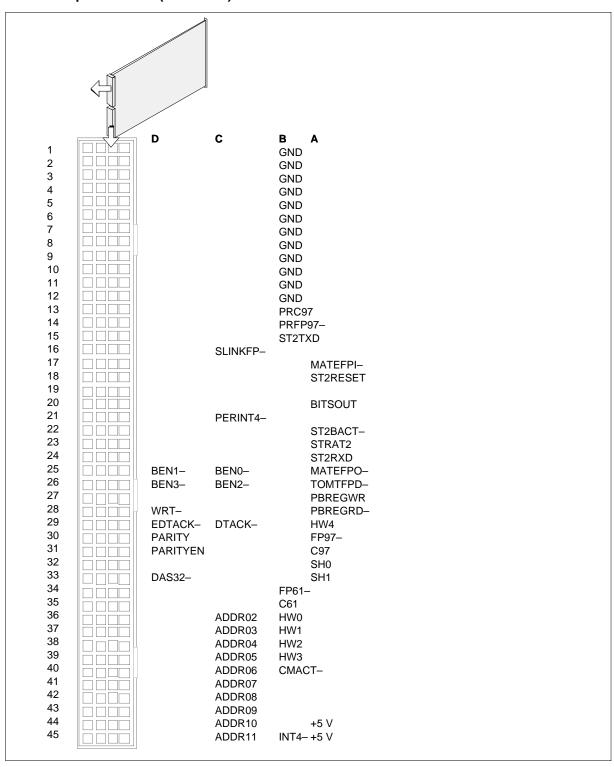

| NT9X53AB | 4-518 |

| NT9X53AC | 4-525 |

|          |       |

| NT9X53AD | 4-532 |

| NT9X54AA | 4-540 |

| NT9X54AC | 4-545 |

| NT9X54AD | 4-551 |

| NT9X62AA | 4-557 |

| NT9X62BA | 4-571 |

| NT9X62BA | 4-577 |

|          |       |

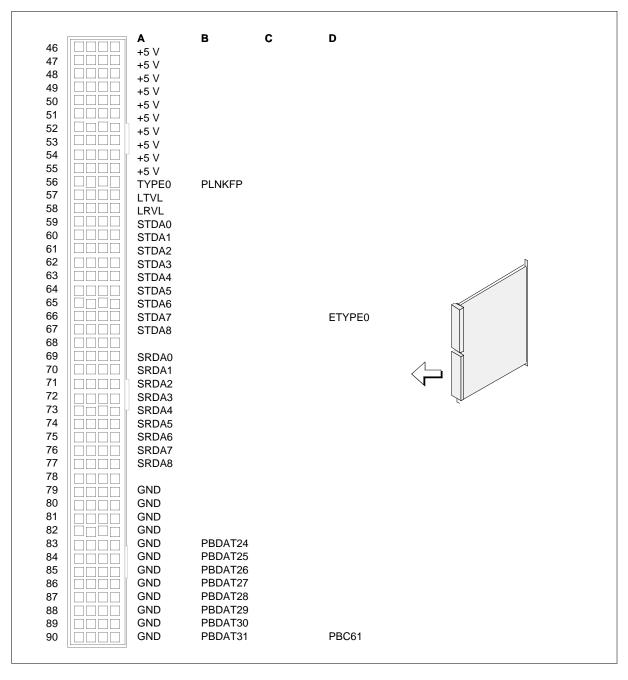

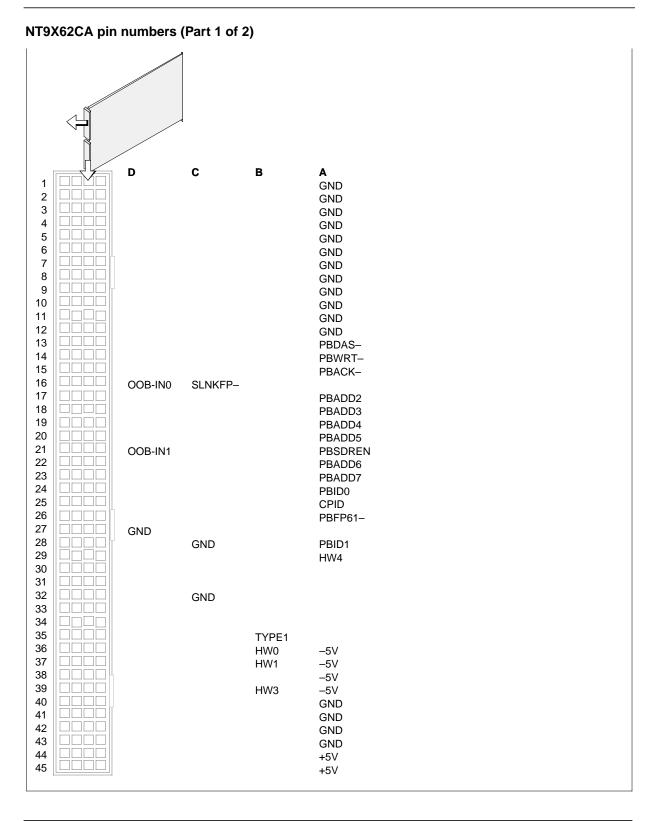

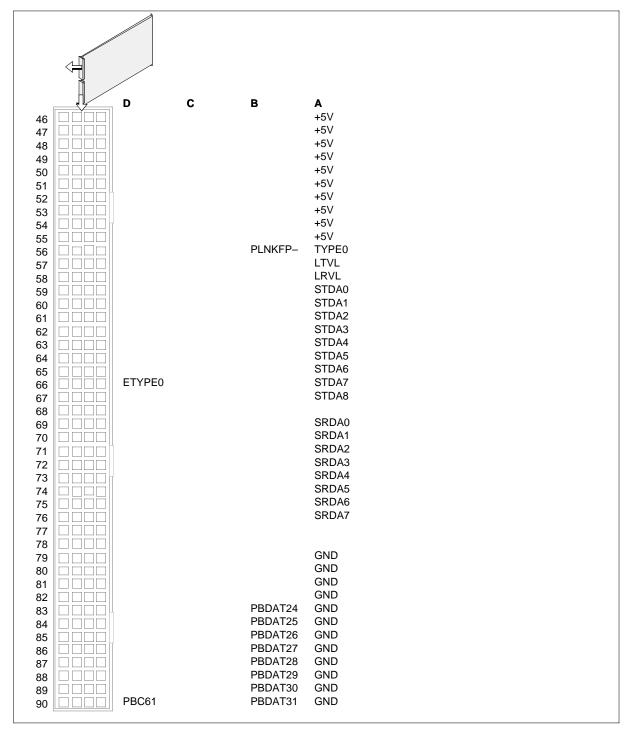

| NT9X62CA | 4-584 |

| NT9X69AA | 4-591 |

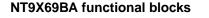

| NT9X69BA | 4-601 |

| NT9X70AA | 4-614 |

| NT9X70BA | 4-619 |

| NT9X70BB | 4-624 |

|          | 7 027 |

|          |       |

| NT9X70CA | 4-629 |

|----------|-------|

| NT9X71AA | 4-635 |

| NT9X71AB | 4-640 |

| NT9X71AC | 4-645 |

| NT9X72AA | 4-652 |

| NT9X72AC | 4-656 |

| NT9X72AD | 4-664 |

| NT9X73AA | 4-671 |

| NT9X73BA | 4-679 |

| NT9X73BB | 4-683 |

| NT9X74AA | 4-689 |

| NT9X74BA | 4-697 |

## 1 NT6Xnnaa (continued)

NT6X69DA through NT6X99AA (continued from Vol. 3)

## NT6X69DA

#### **Product description**

The NT6X69DA replaces the NT6X43DA message interface card in the international market. The NT6X69 has the capabilities of the NT6X43. The NT6X69 can process message protocols.

### **Functional description**

#### Functional blocks

The NT6X69DA contains the following functional blocks:

- parallel speech bus (SB) message interface

- SB connection memory (CM)

- inter module connection (IMC) interface

- interrupt generator

- tone generator

- protocol processor (PP)

- signaling processor (SP) and PP shared memory

- shelf reset generator

- cyclic redundancy check (CRC) ROM

- process timing ROM

- SP interface

- power-up circuits

#### Parallel speech bus message interface

The parallel SB message interface in the NT6X69 differs from the SB message interface in the NT6X43. In the NT6X43, the asynchronous SP sends messages on the synchronous SB. The system requires circuits that synchronize. Synchronizing circuits consist of a frame level interrupt and a double buffer. In the NT6X69, the synchronous PP sends the message so that all the NT6X69 needs is the following. The NT6X69 needs a transmit (Tx) RAM and holding registers, and a receive (Rx) RAM and holding registers. The holding register pairs are the outgoing SB Tx/Rx pair and the IMC Tx/Rx pair. The CM controls gating of register output for each time slot. The system dedicates the first half of the instruction to PP to write to Tx RAM or to read from Rx RAM. In the second half, data latches in the Tx holding register from the Tx RAM according to the port/channel counter. The system writes data to the Rx RAM from the Rx holding register.

#### NT6X69DA (continued)

#### Speech bus connection memory

The CM arbitrates the access of different service cards to the SB on a time slot condition. The SP accesses the CM in the same way as the SP and PP shared memory. The PP cannot access the CM. In the first half of the instruction cycle, the port/channel counter addresses the CM. The data latches to a holding register. The data in the holding register addresses CM decoding PROM. This action enables the tone driver, SB drivers and receivers, and an IMC register on the NT6X69. Two bits from the holding register are fed to the formatter and the time switch through the backplane. Three other bits from the holding register are accessible through spare slots on the backplane.

*Note:* T bits are not identical to the bits of the NT6X43 card. There are more functions in the decoding circuits like IMC messaging and the tone checksum.

#### Intermodule connection interface

The IMC interface provides a 64 kbps link to the mate unit. The link appears to the PP as an SB time slot. The SP assigns the time slot through the CM.

The IMC circuits is a shift register loaded with data. The IMC holding register loads the data in the SB interface when the CM enables the SB. Data exchanges occur between the two shelves during the active channel 0 (CH0) time. The active clock gates the data exchange. The system can assign the IMC time slot away from the CH0 time to avoid data corruption. The IMC link does not use the SB. The IMC time slot on the SB is available for pulse code modulation (PCM) or tones.

Errors can occur with the IMC link when the two shelves are out of synchronization. The reasons for these errors are as follows:

- The CM circuits on the inactive unit runs on the inactive clock. If the units slip, the inactive IMC time slot can occur at the active CH0 time.

- The PP is frame synchronized to the PP shelf. The PP can miss or double-read the register when the units slip.

#### Interrupt generator

The system provides interrupt generation for the PP to signal to the SP. The interrupt generation relieves the SP from polling the message queue pointers. The PP can access the INTSTB strobe to initiate a level 4 interrupt.

#### **Tone generator**

Tone generation circuits on the NT6X69 card contain the R09 generating chip, the tone PROM, and the tone holding register. The system maps T0, T1, and T2 bits from the connection memory to two tone control bits on the R09. The

#### NT6X69DA (continued)

system maps the bits to specify the type of time slot. Eight–bit data from the R09 latches to the holding register. The CM circuits control gating of the contents of the holding register to the outgoing SB.

#### **Protocol processor**

A 32–bit instruction from microstore ROM latches to the micro–instruction register every processor cycle. The micro–instruction register controls the following:

- CPU

- CPU data multiplexer

- zero/not-zero conditional code

- skip instruction decoder

- destination/source (DEST/SRC) decoder

- sequencer

- sequencer data multiplexer

The CPU receives instructions from the instruction register (INST REG). The CPU produces an 8-bit result on the designation bus and a 1-bit zero conditional code. Direct data input from the multiplexer can be from the INST REG for immediate data. Direct data from the muliplexer can be from the SRC bus for external data. Data beginning depends on the instruction type. The DEST/SRC decoders arbitrate the different external registers that put data on the SRC bus, and provide strobes to other registers. This condition allows one register to receive data from the DEST bus. The firmware uses two of the DEST strobes to aid tests. The CPU produces a conditional code. This code can toggle and depends on bit 0 of the micro-instruction register. The conditional code that results feeds to the sequencer and to the skip instruction decoder. Sequencer control ROM translates the four bits from the instruction register, the reset bit, and the skip bit. The sequencer control ROM formulates a 4-bit instruction fed to the sequencer. The skip instruction decoder examines bits 1 to 3 of the micro-instruction register and the conditional code. When the skip condition is valid, the skip bit is set by the suppression of the clock to the CPU. The skip bit is set during the next cycle time, as a result, the CPU internal registers are not updated. The skip bit can be set by the equivalent of a continue instruction from the sequencer control ROM.

The system accesses and executes the next instruction. The system does not store the result. The system cannot skip an instruction. The execution of the first skip instruction sets the skip bit. The execution tells the internal CPU register not to store the result of the next instruction. The second skip instruction executes and sets the skip bit again. Sequencer data can come from the instruction register or from the DEST bus. Where the sequencer data comes from depends on the instruction bit that controls the multiplexer. Output of the sequencer addresses microstore ROM that produces the next instruction bits that the micro–instruction register catches.

The PP accesses the following functional blocks:

- RAM shared with the SP

- CRC ROM for CRC calculation the DMS-X protocol requires

- process timing ROM, that allows the firmware to synchronize to the frame

- shelf reset generator that allows the PP to initiate a shelf reset from the NT6X46 card

- interrupt generator that allows the PP to initiate a level 4 interrupt to the SP

- network module (NM) interface

- SB interface

- IMC interface

#### SP and PP shared memory

The SP and PP communicate through an 8KX8 block of RAM that the two processors share. This block of shared memory serves as:

- workspace for the PP

- buffer for messages the PP receives for the SP

- buffer for messages the SP queues for the PP

- opcode area

The SP cannot directly apply the NM interface, the SB interface and other interfaces. The PP firmware provides a set of opcodes that allow the SP to apply these interfaces indirectly.

The first half of the instruction cycle is for PP read and write access. The first half of the cycle makes the access of this RAM transparent to the PP and the SP. The second half of the cycle is for access by the SP interface. Both processors have read and write access over the complete address range of the memory. When the system performs a memory test for one processor, the other processor must not write the memory.

#### NT6X69DA (continued)

#### Shelf reset generator

The PP performs the following sequence to initiate a shelf reset:

- 1. The PP accesses the auxiliary reset strobe to clock the reset flip–flop.

- 2. Output of the reset flip–flop is driven to the backplane and connects to the NT6X46 card.

- 3. The NT6X46 card ceases activity and issues the module reset signal to the rest of the shelf to acknowledge the reset.

- 4. The module reset the NT6X46 card issues clears the reset flip–flop on the NT6X69 card.

#### Cyclic redundancy check ROM

The CRC ROM has two tables. Each table contains 256 bytes. A two-stage CRC accumulation process uses these tables.

#### Process timing ROM

Process timing ROM allows the PP to synchronize each process time slot for the frame limit. The port/channel counter addresses PROM that the PP can read at any instruction cycle.

#### Signaling processor interface

The SP memory map is standard on the cards that interface to the SP. Address and control signals are buffered. An access sequence synchronizes SP requests and generates a read or write access cycle. This condition occurs when a valid address falls in the range that the system assigns to this card type. The interface is asynchronous and an acknowledge signal indicates the end of the access cycle.

#### **Power-up circuits**

A simple recording completing (RC) circuit resets the firmware and clears the interrupt generator and auxiliary reset flip–flops during power–up.

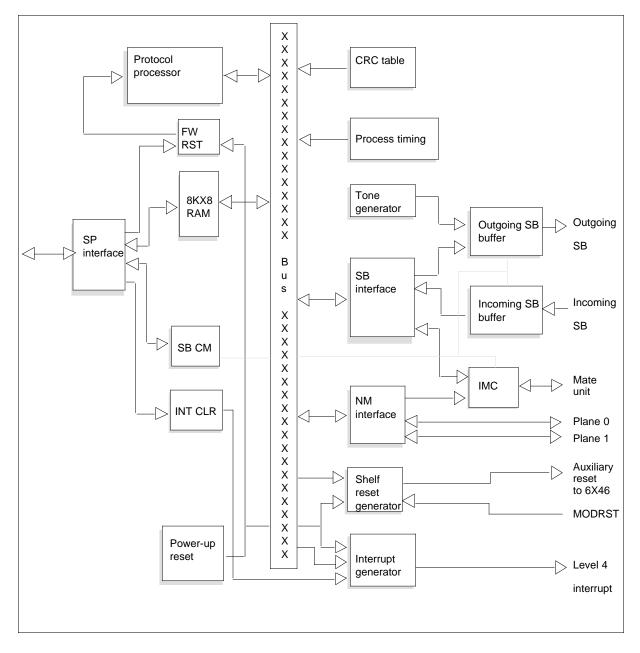

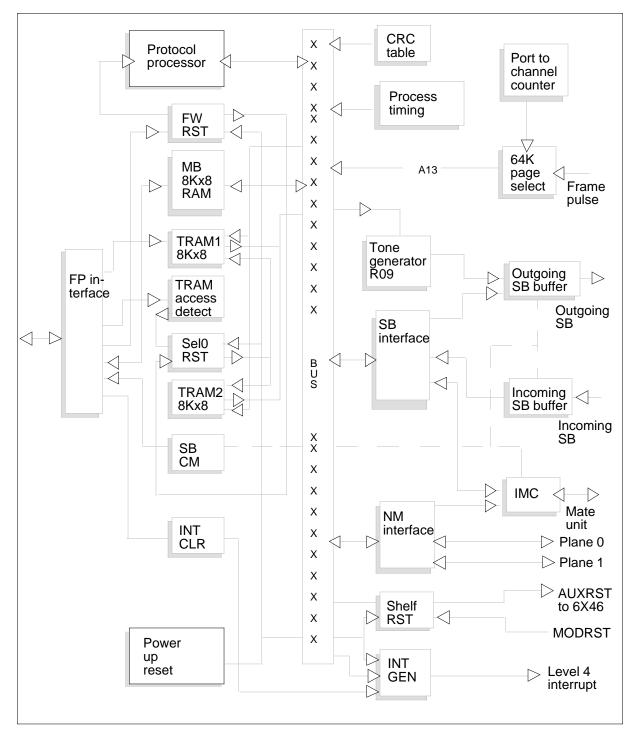

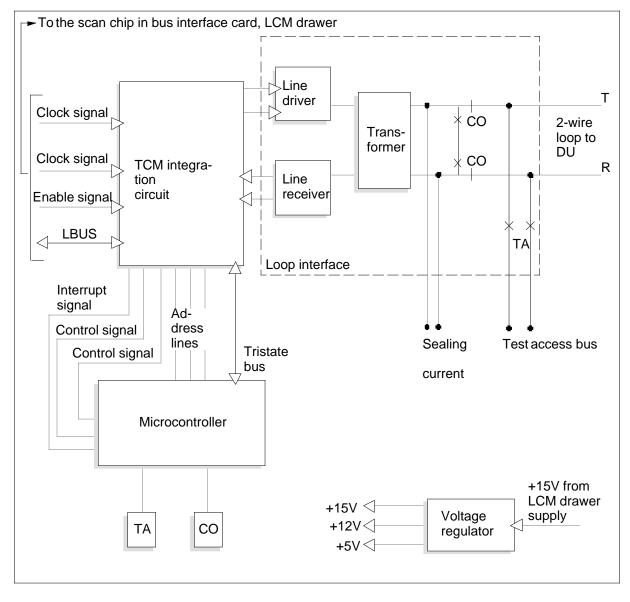

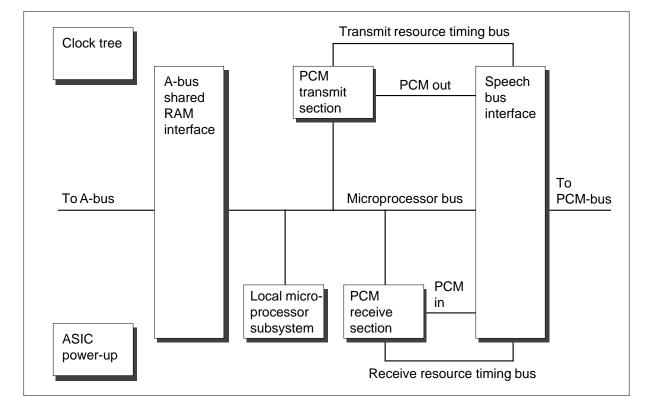

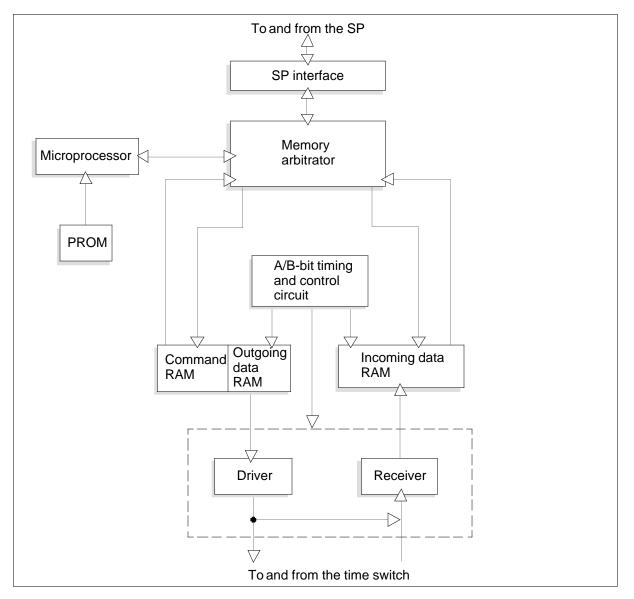

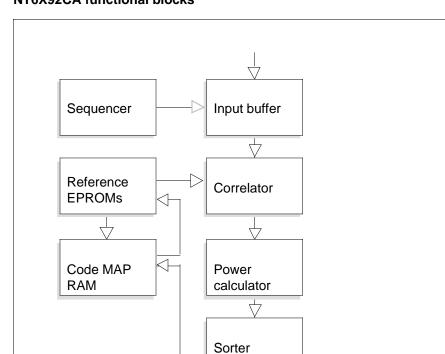

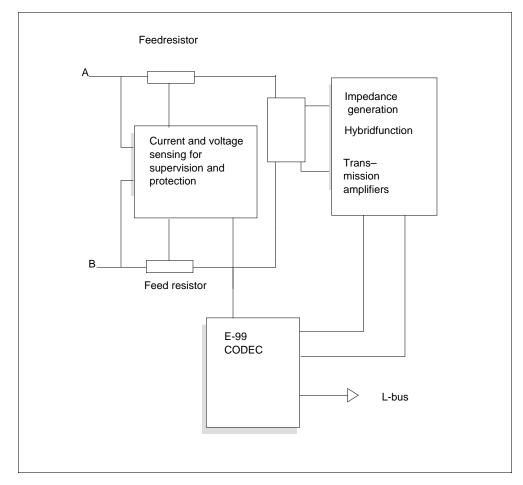

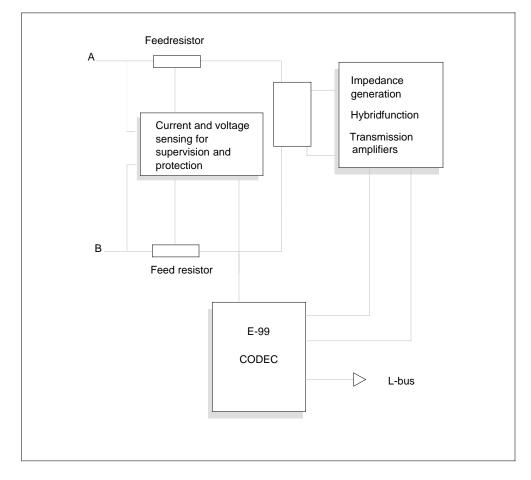

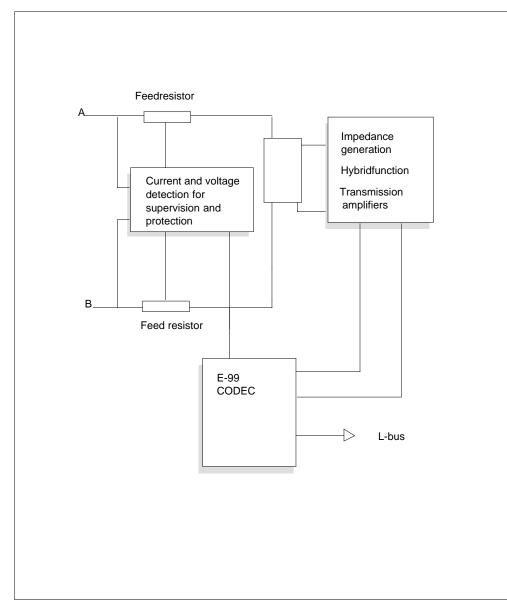

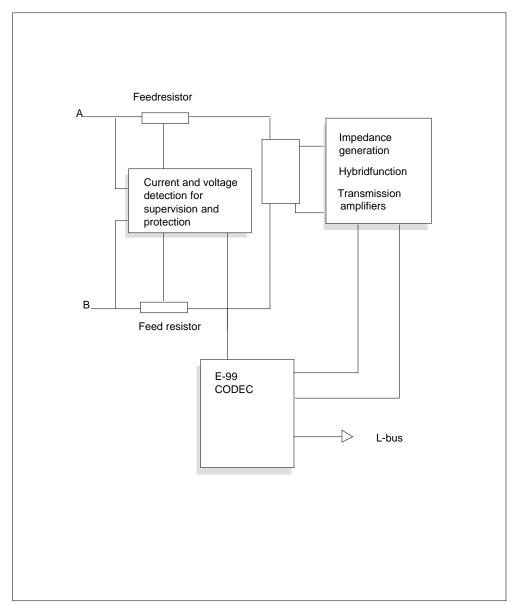

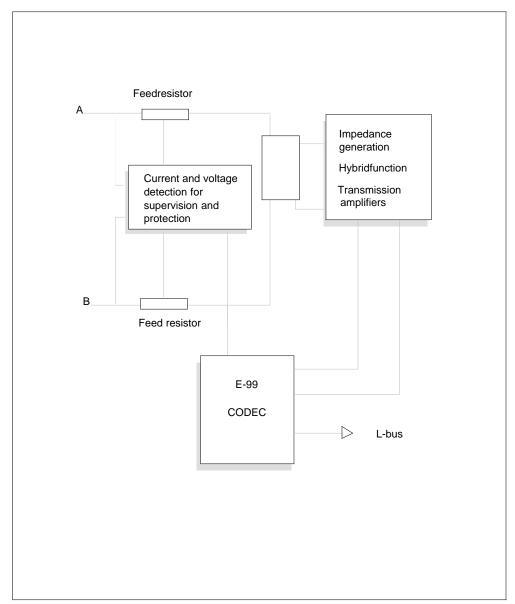

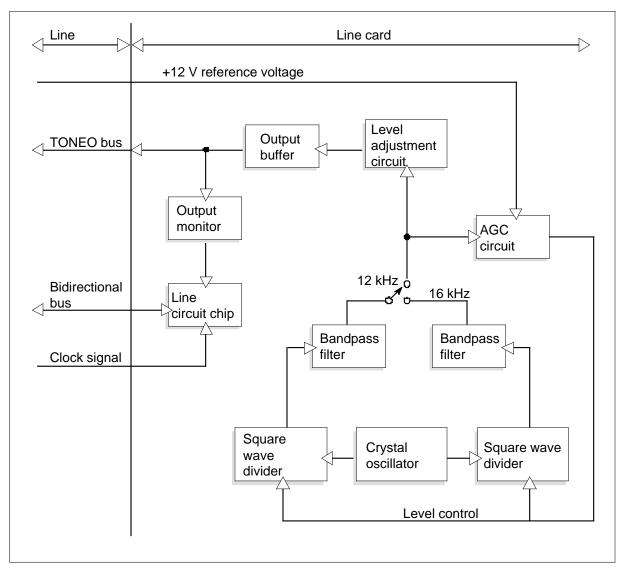

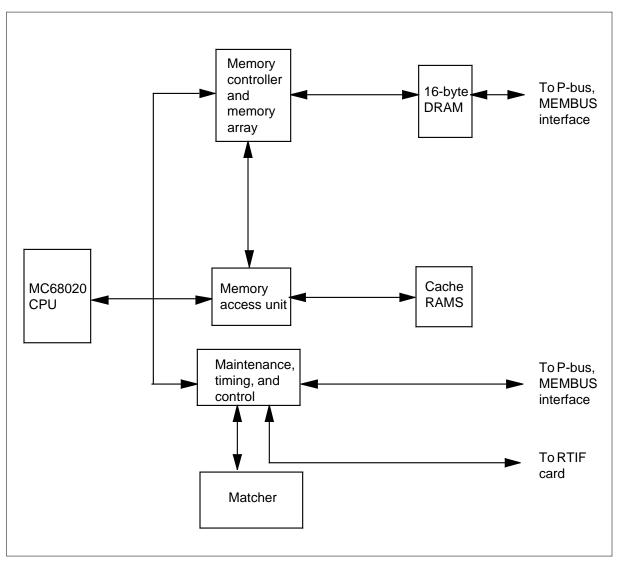

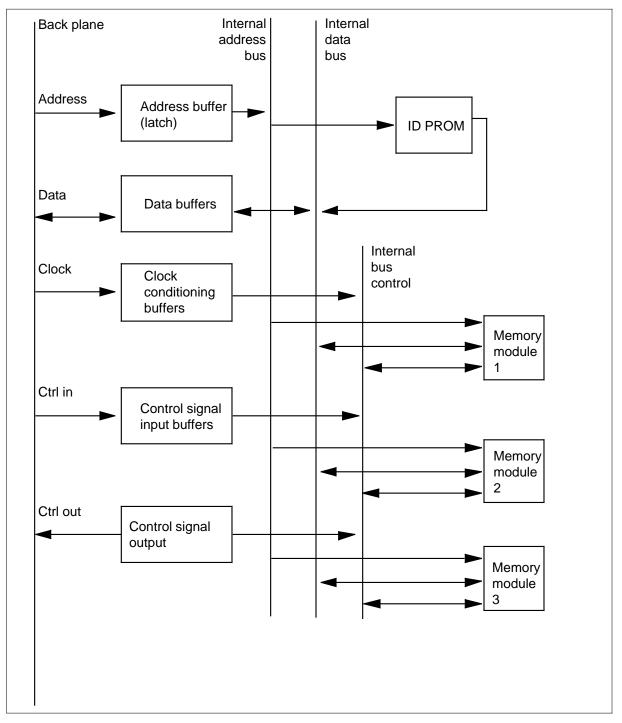

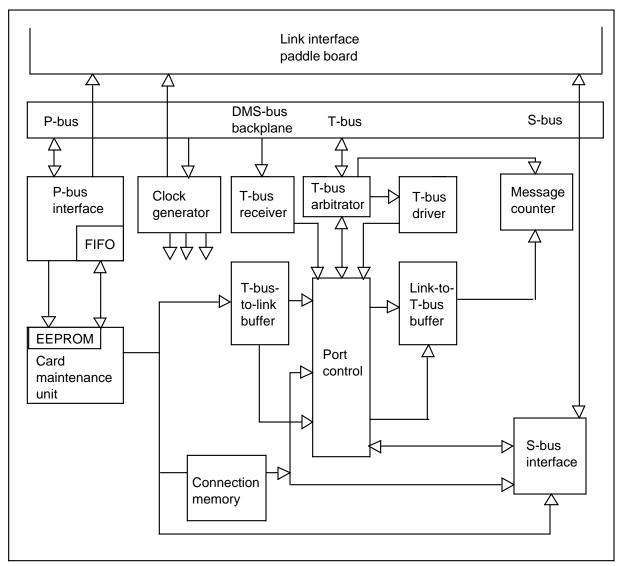

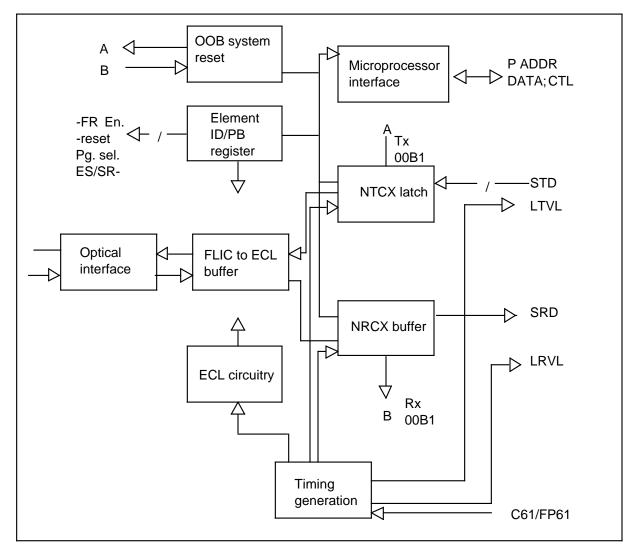

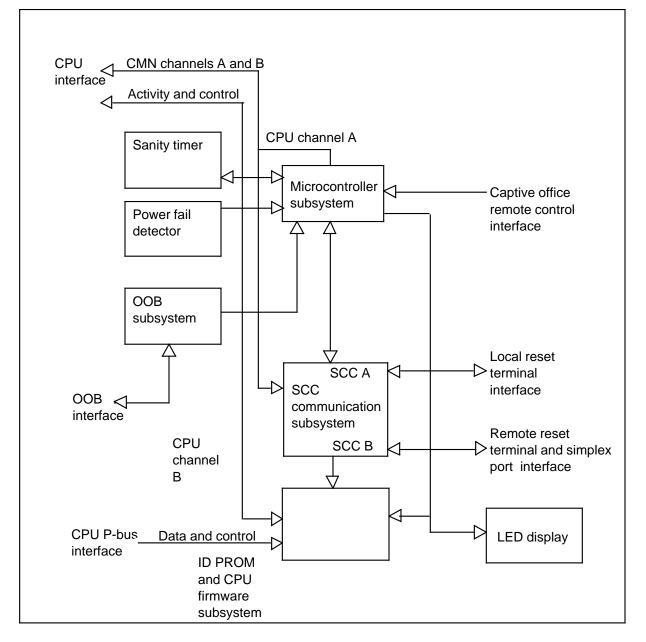

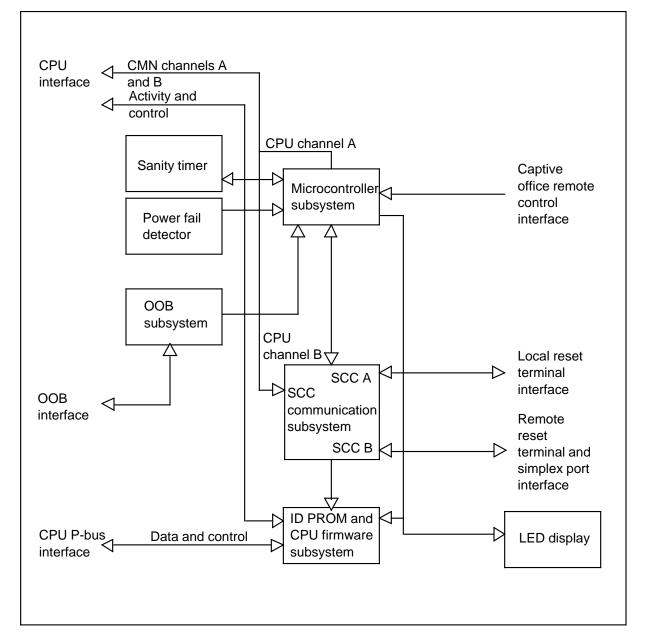

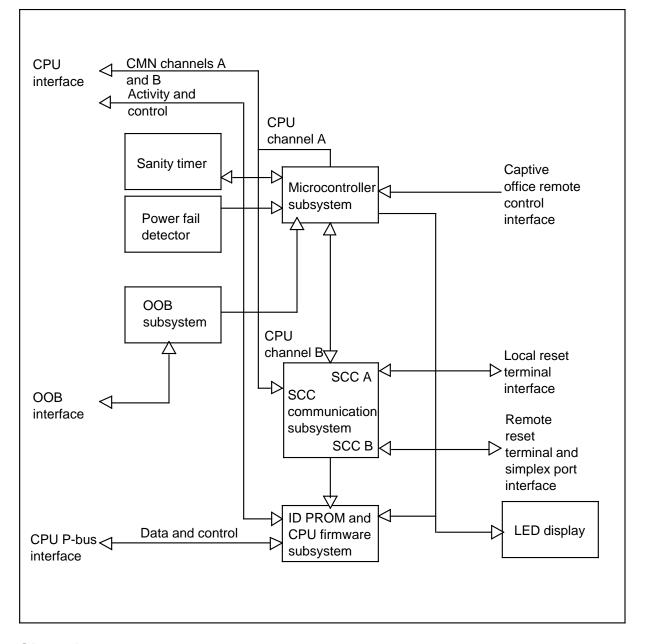

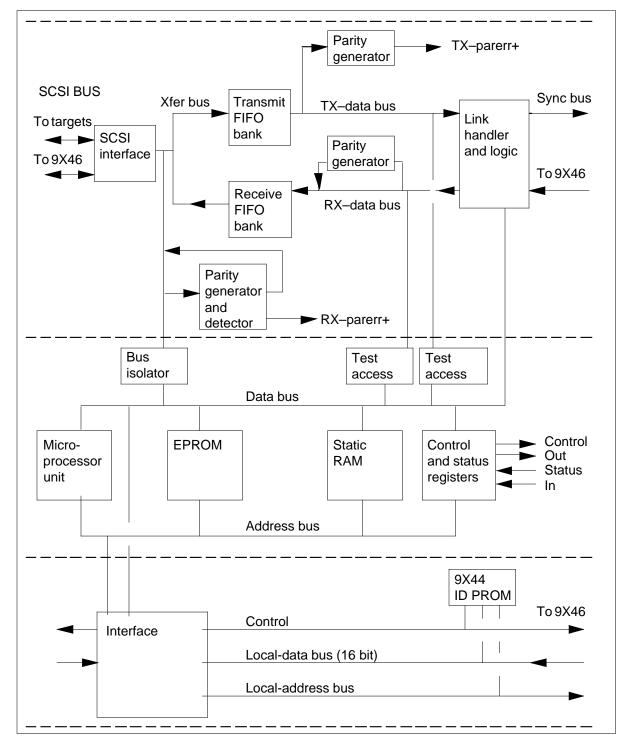

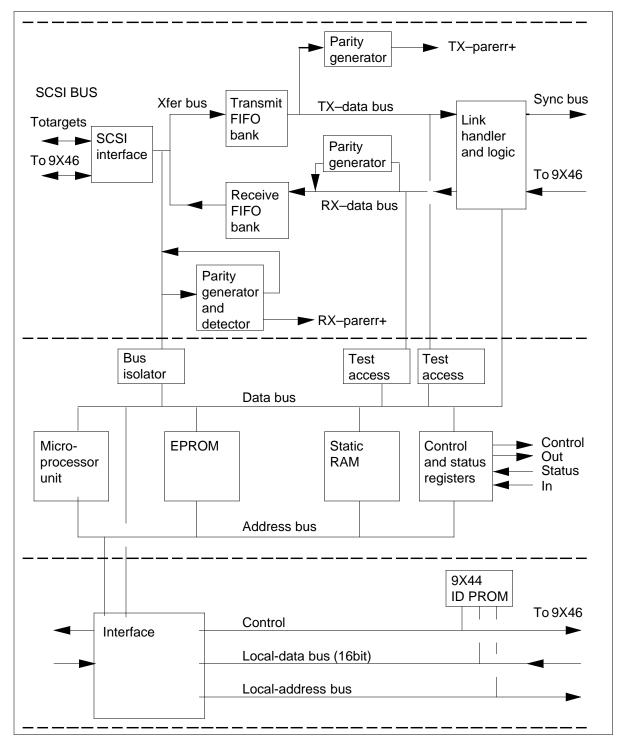

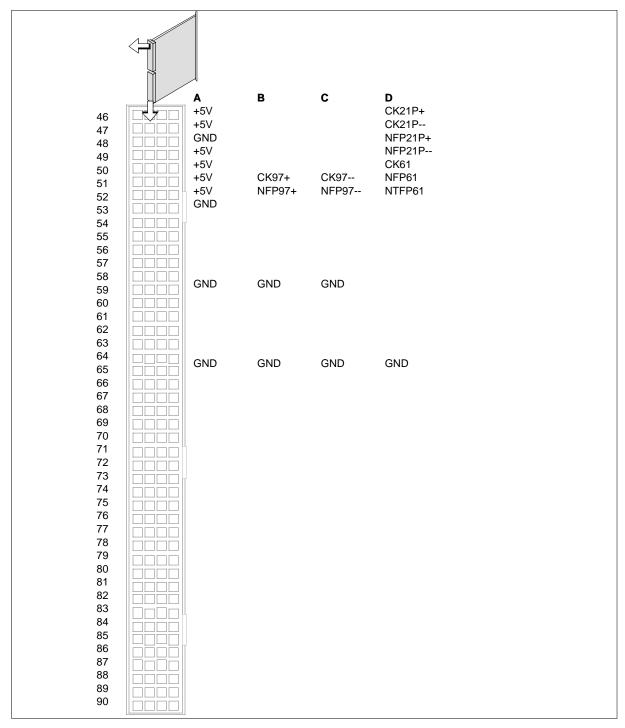

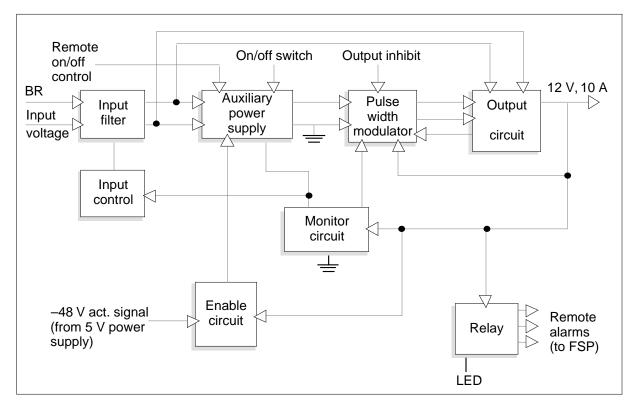

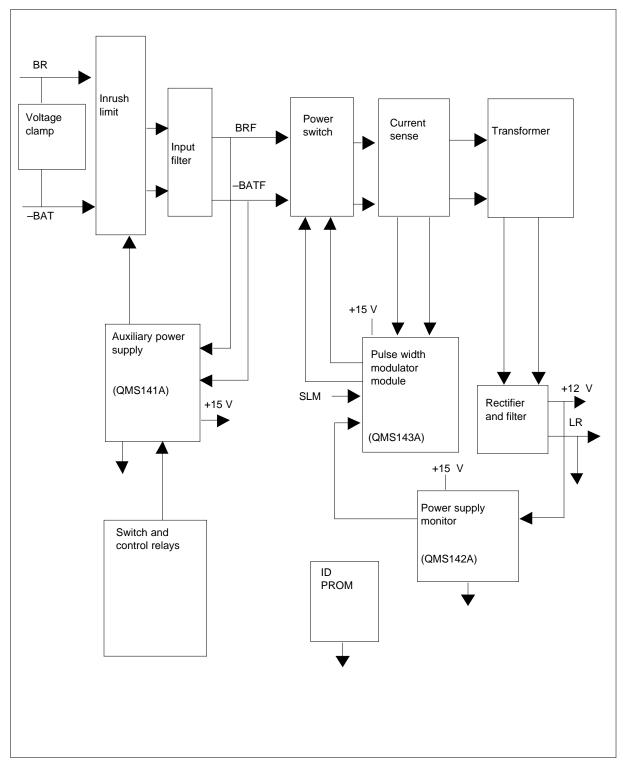

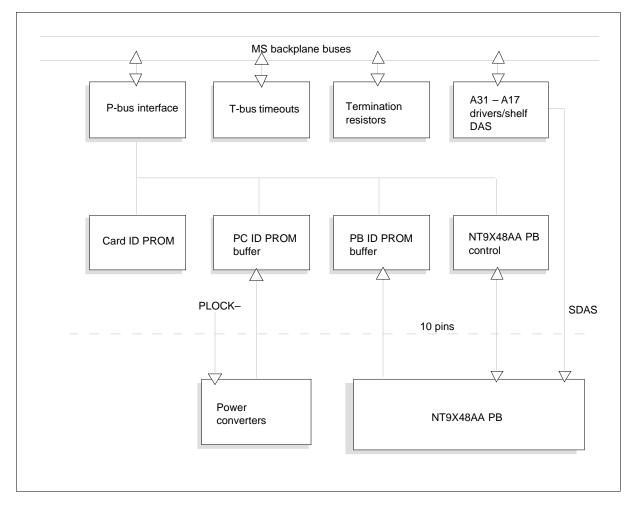

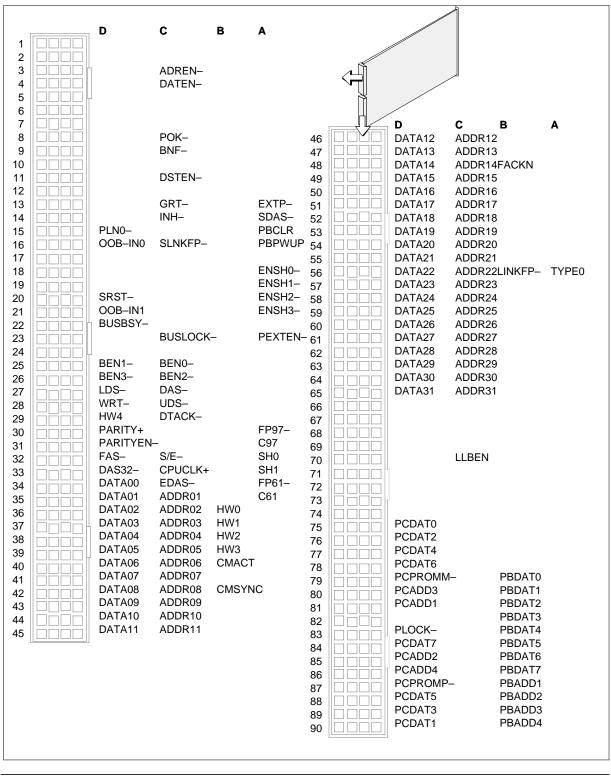

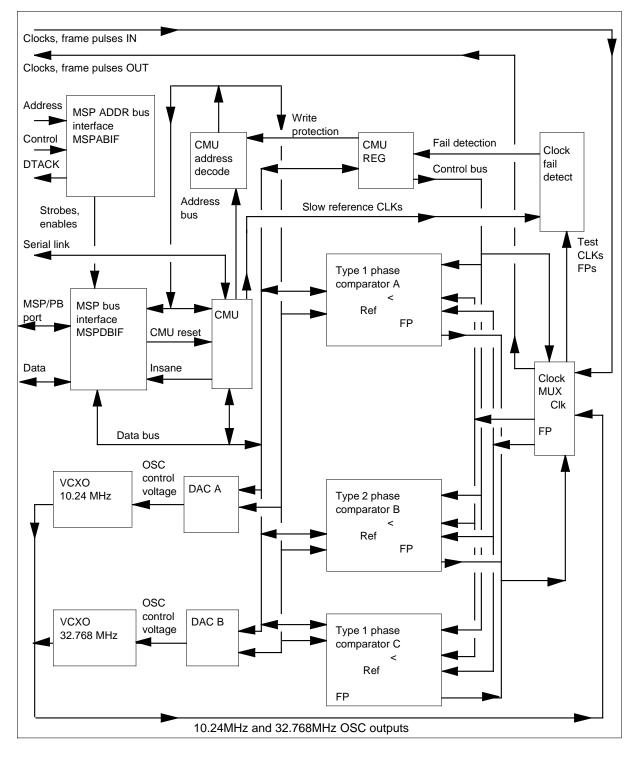

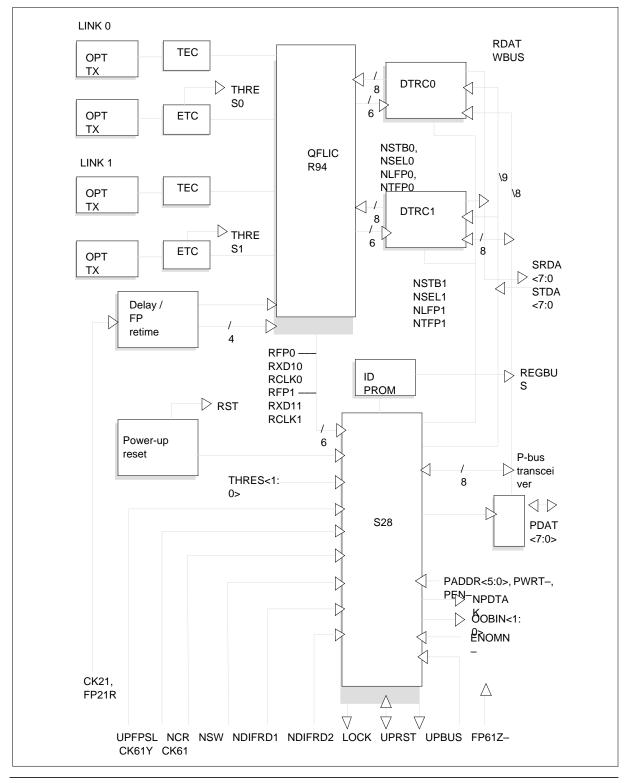

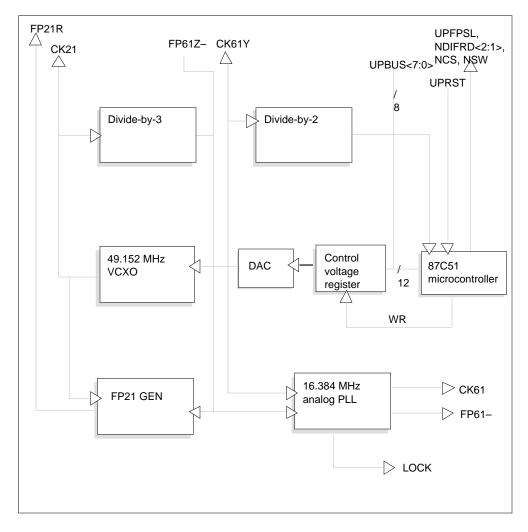

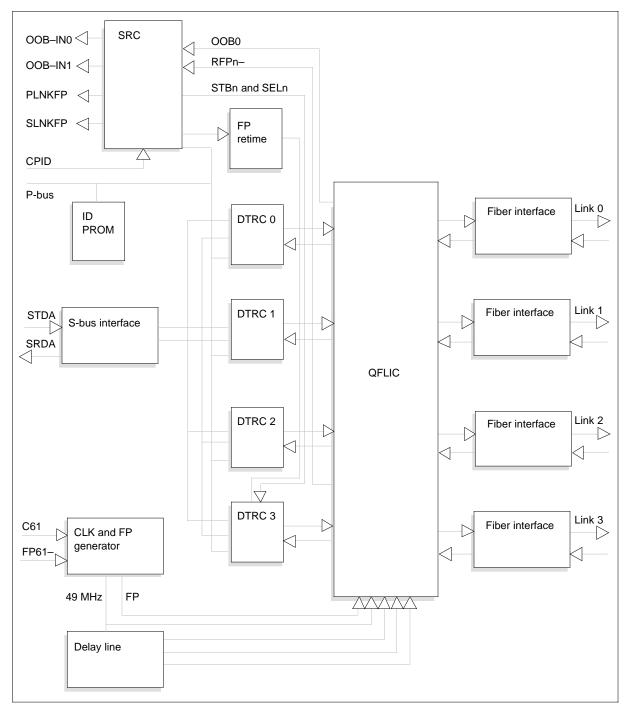

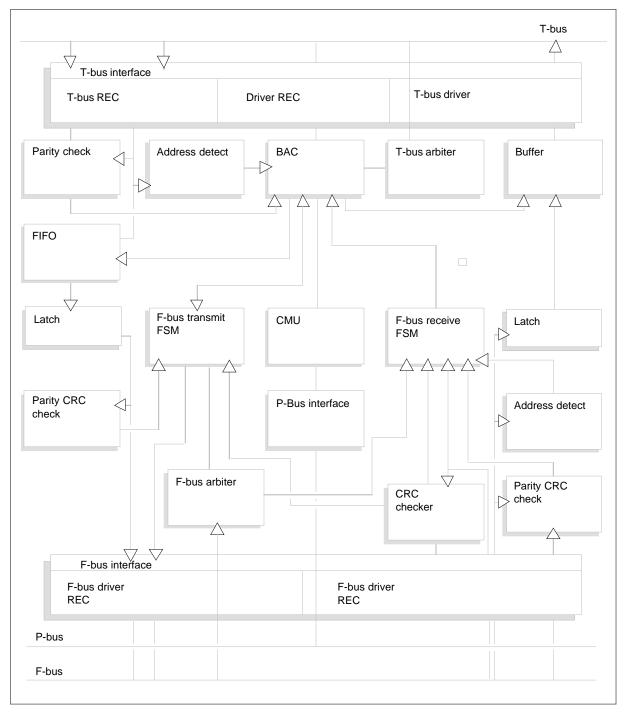

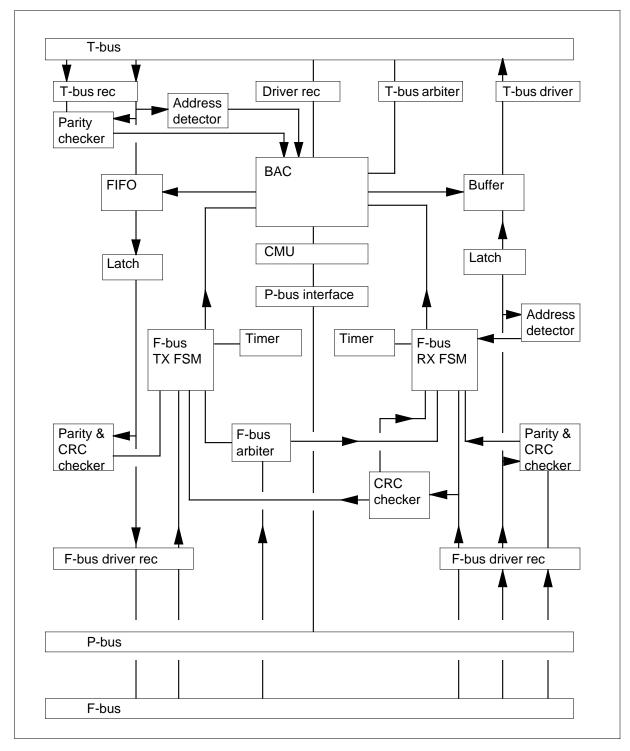

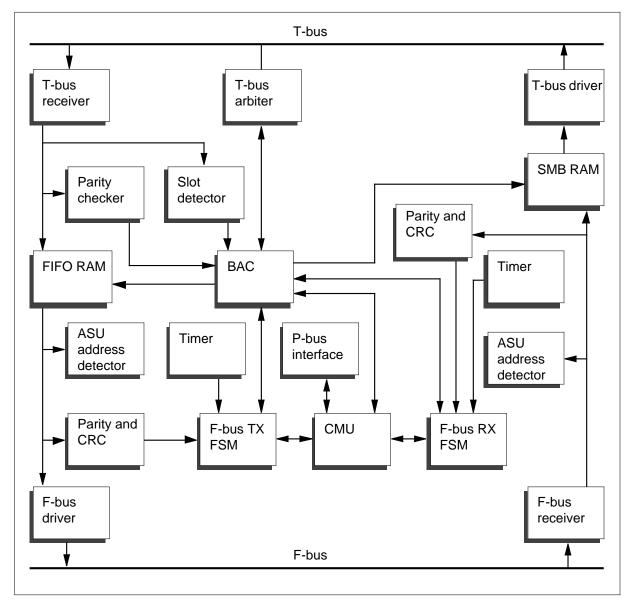

The working relationship between the above blocks appears in the following figure.

## NT6X69DA (continued)

#### NT6X69DA functional blocks

## Signaling

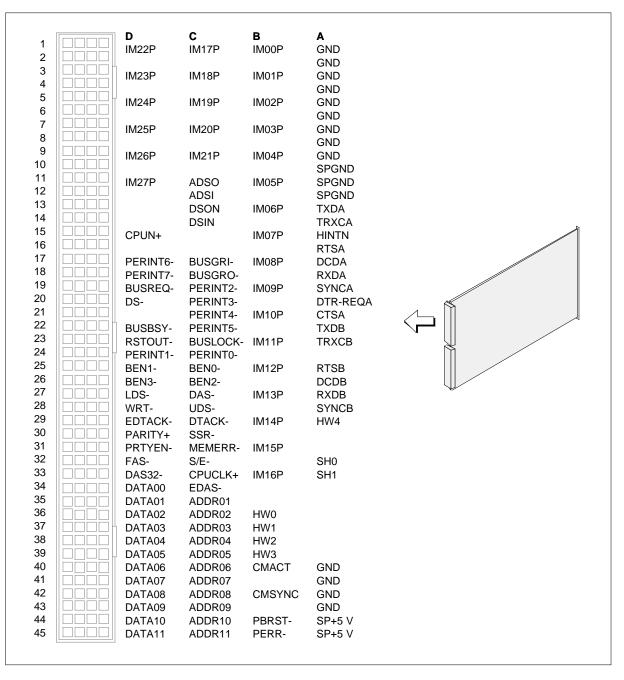

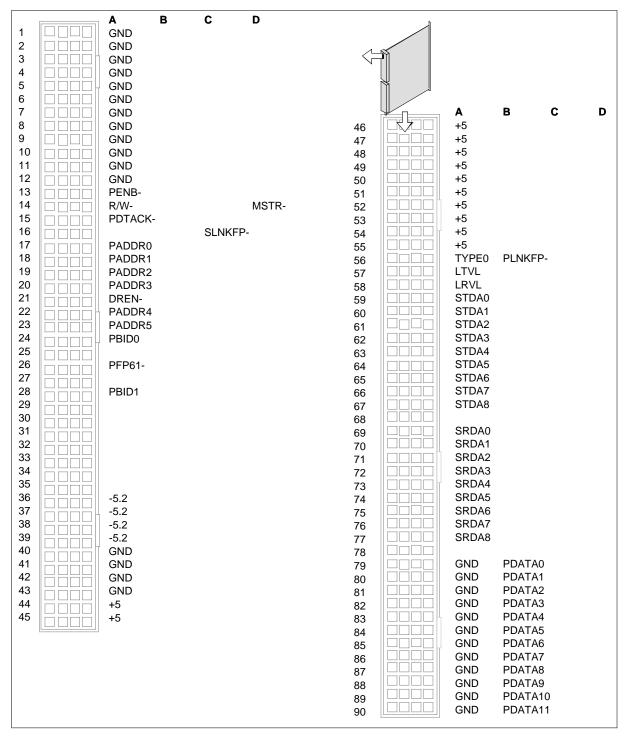

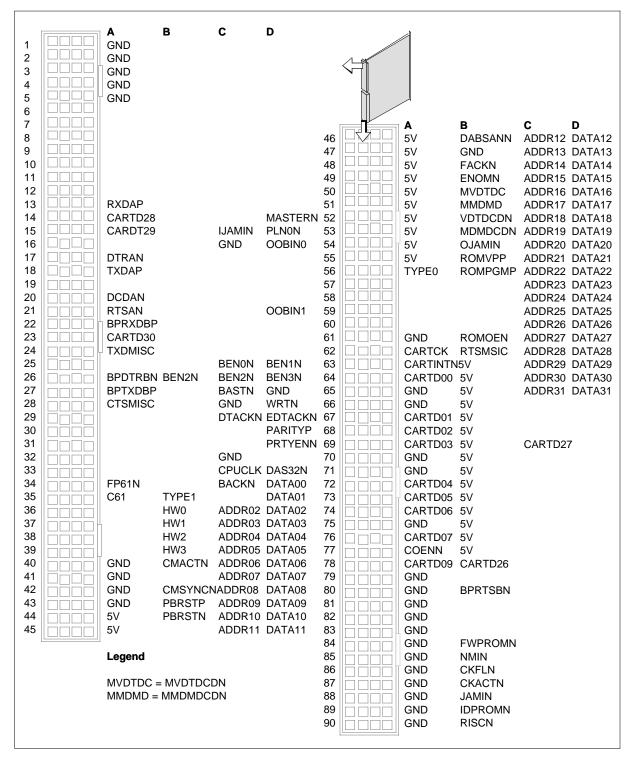

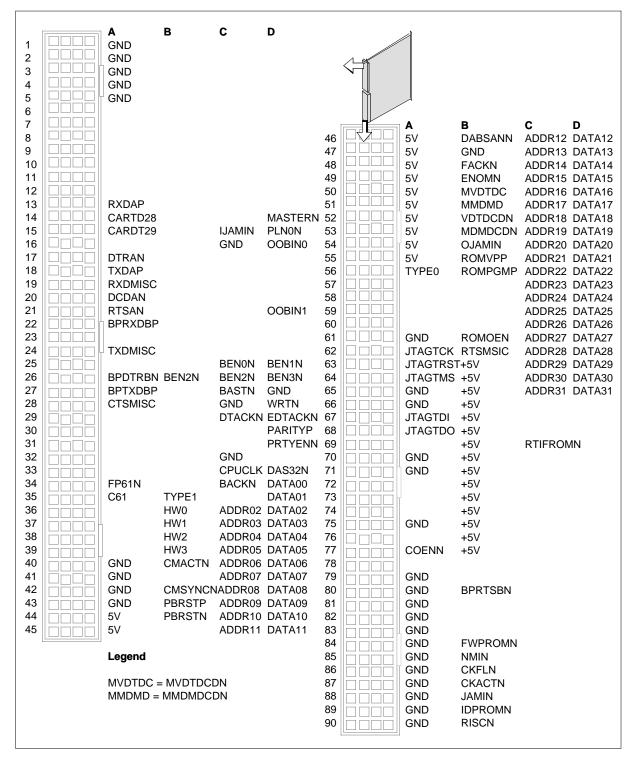

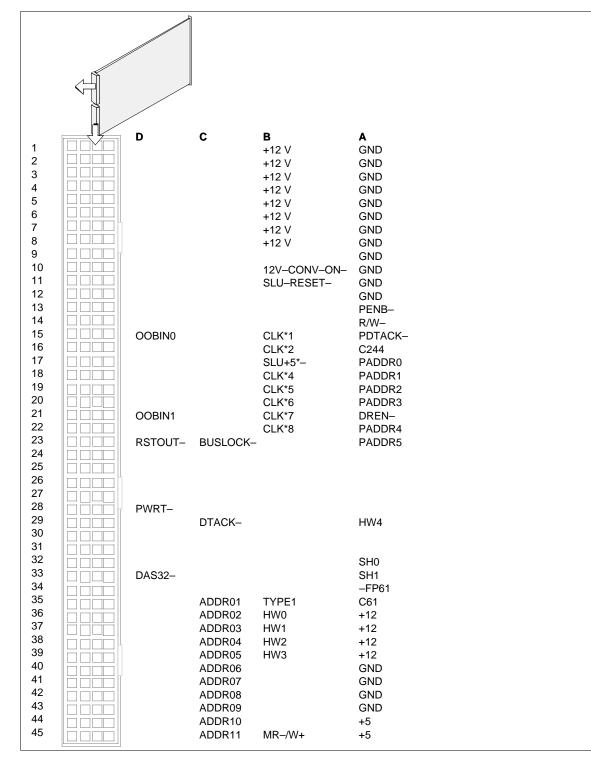

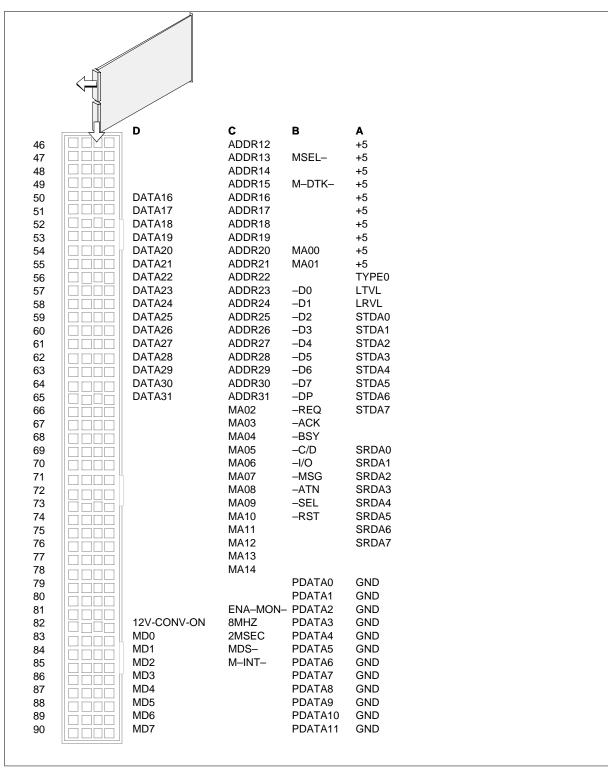

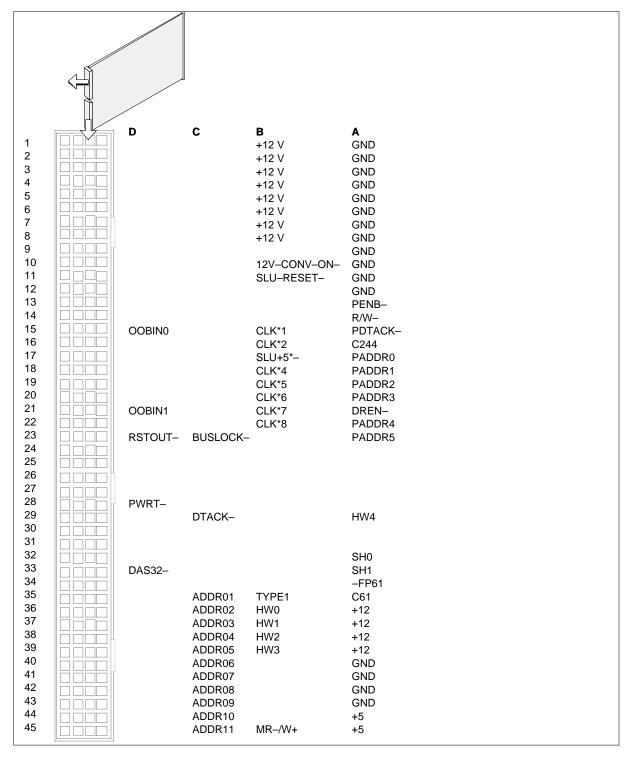

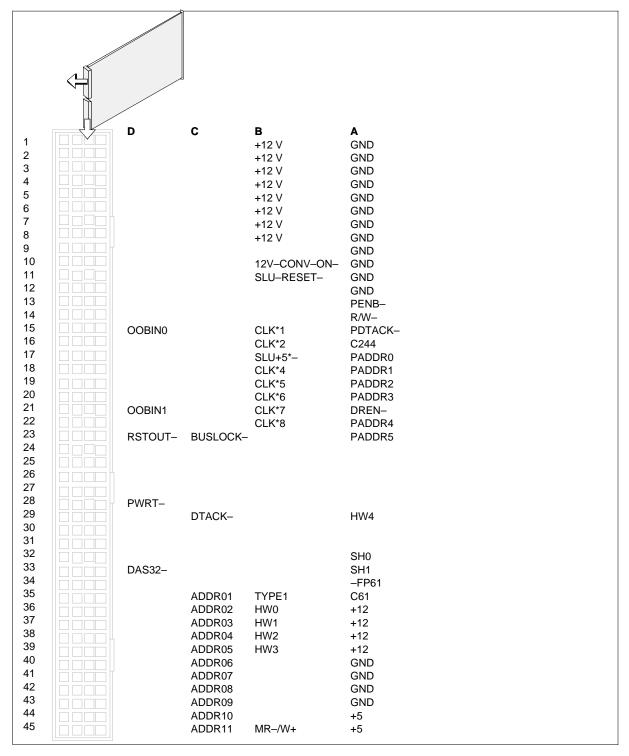

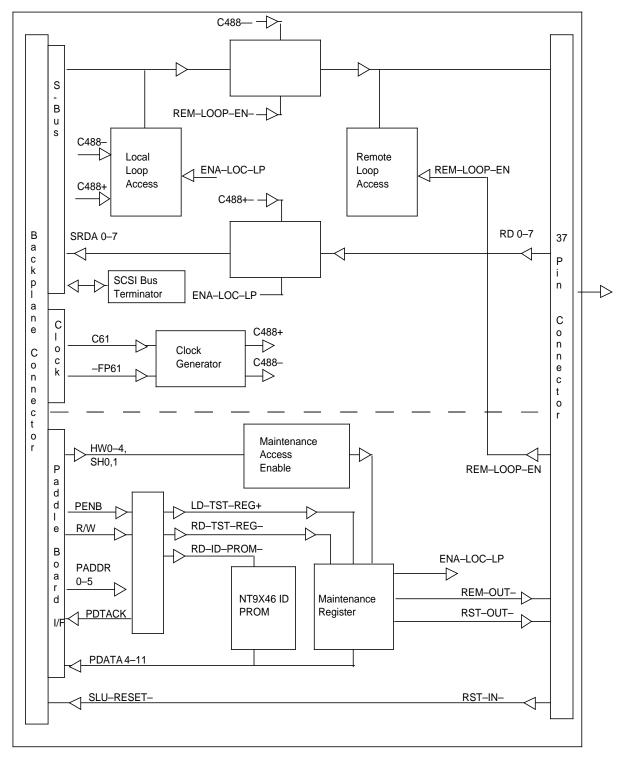

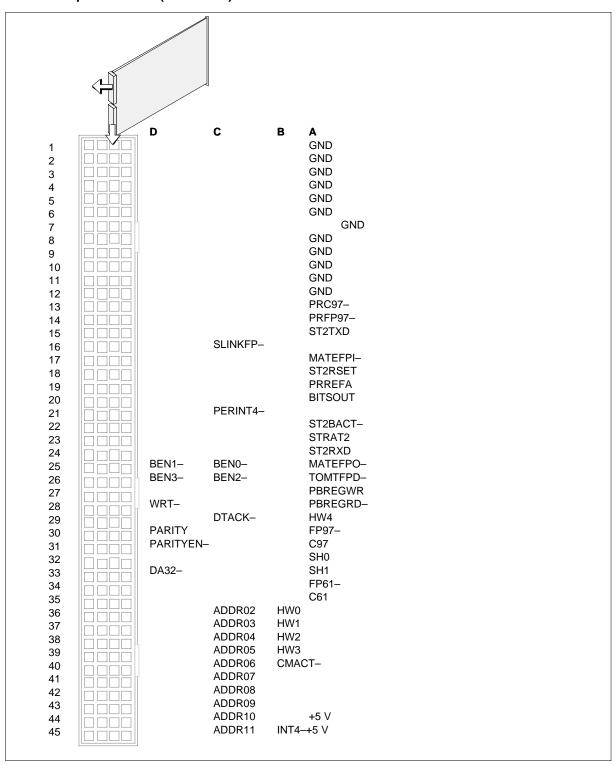

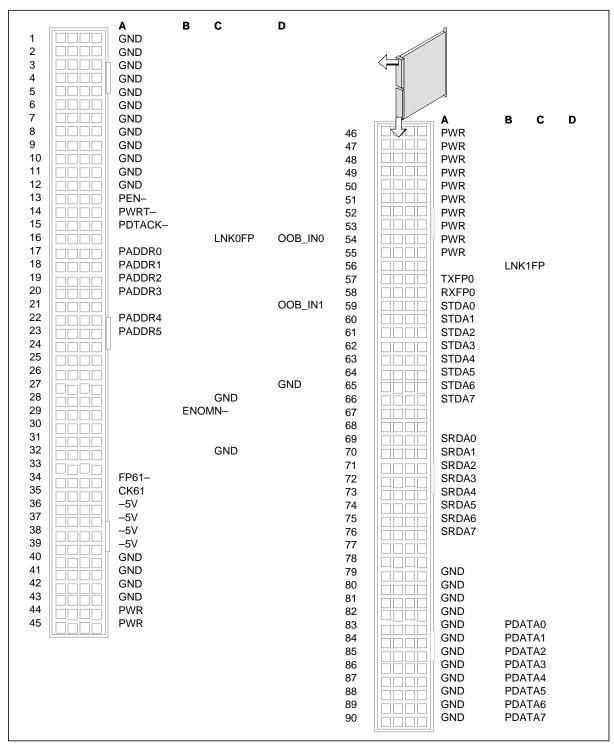

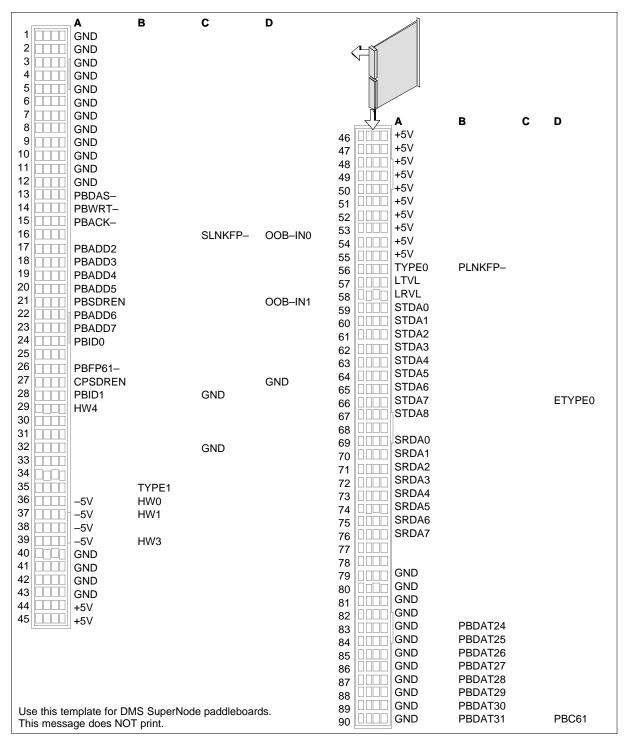

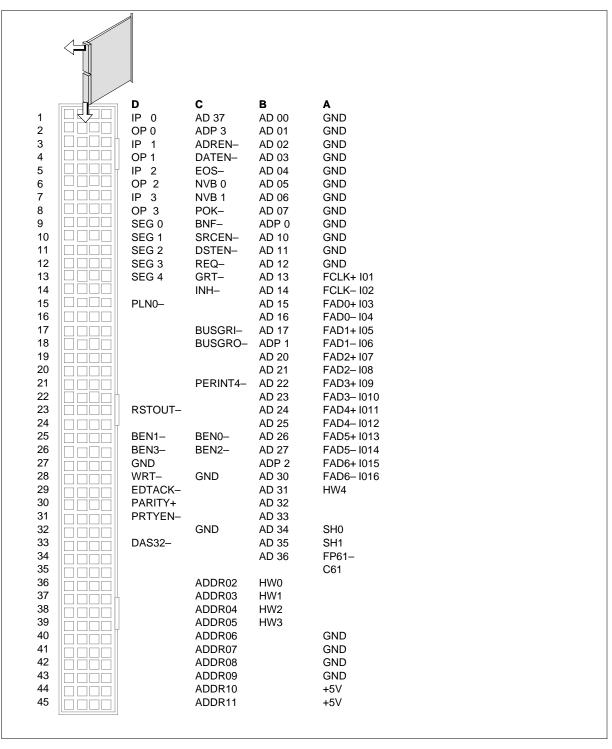

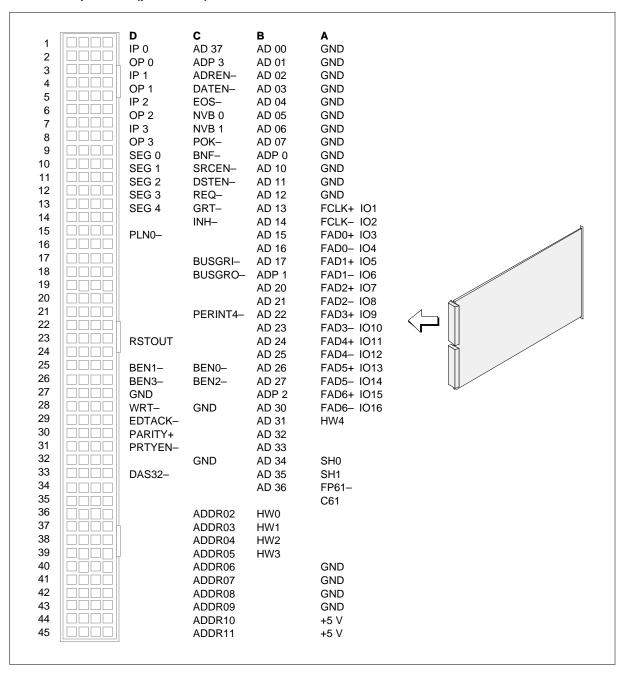

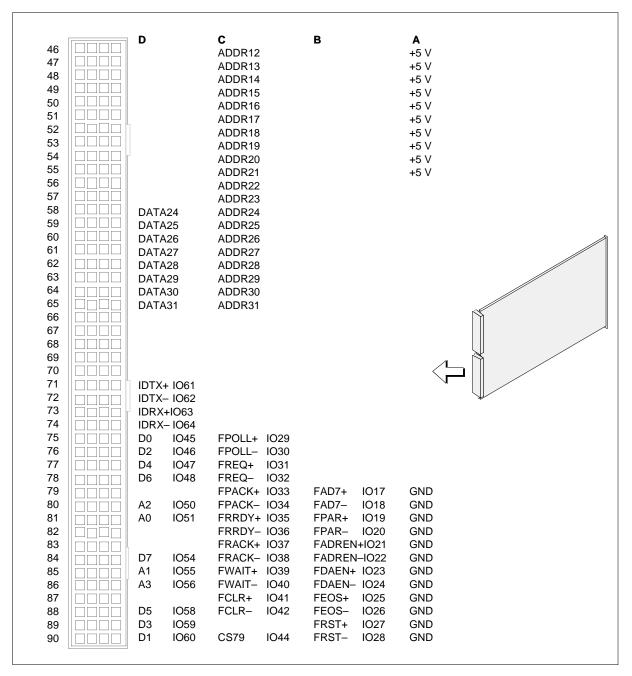

#### **Pin numbers**

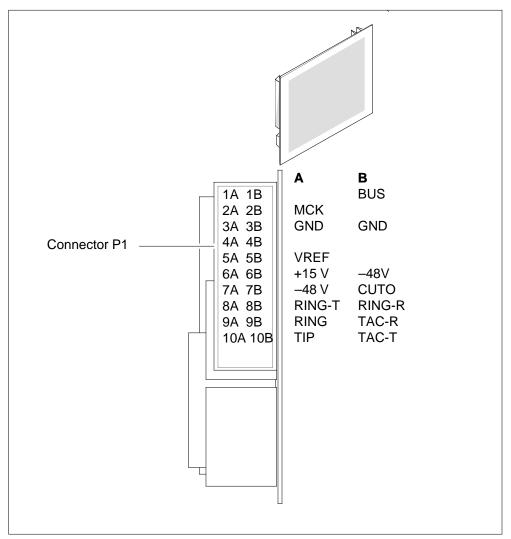

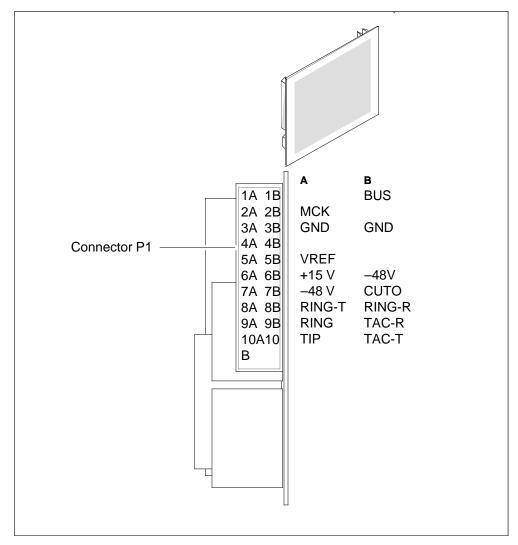

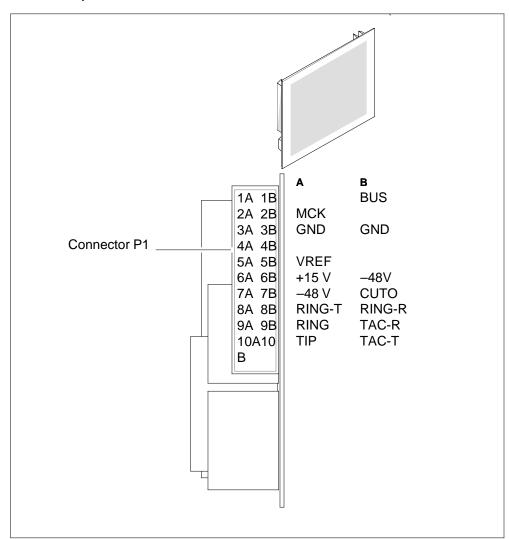

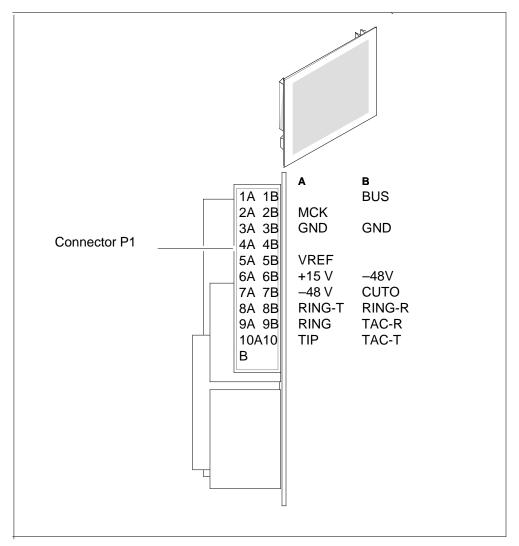

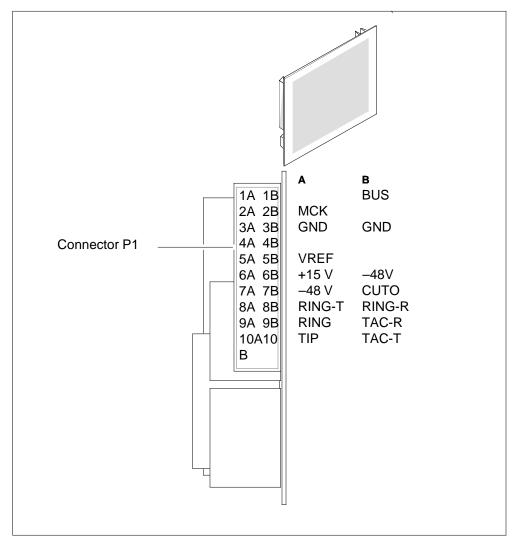

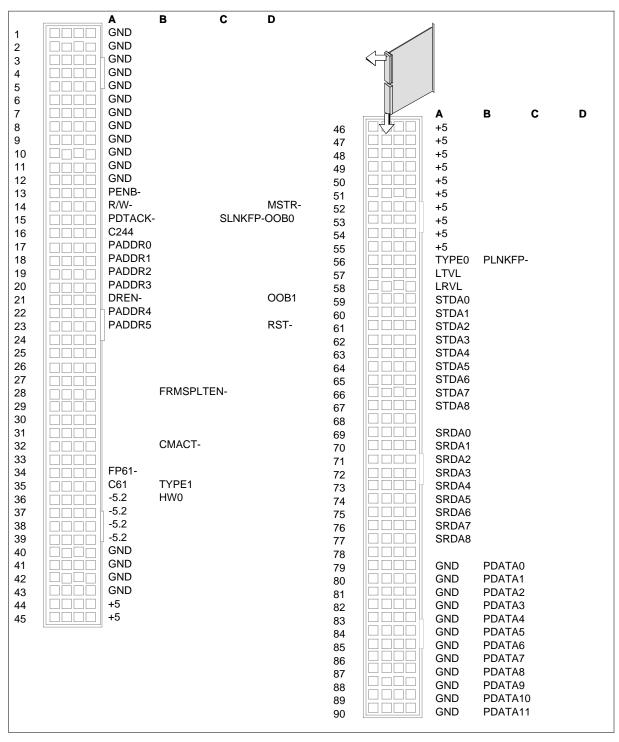

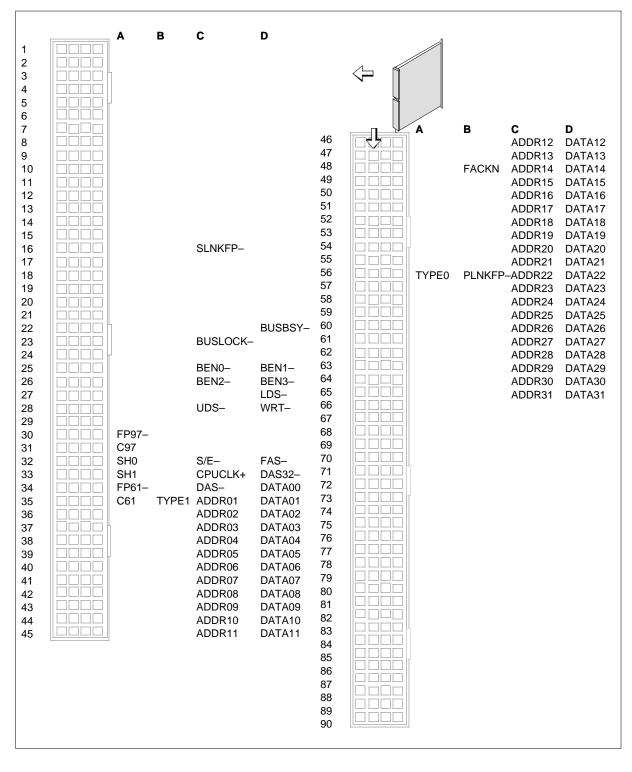

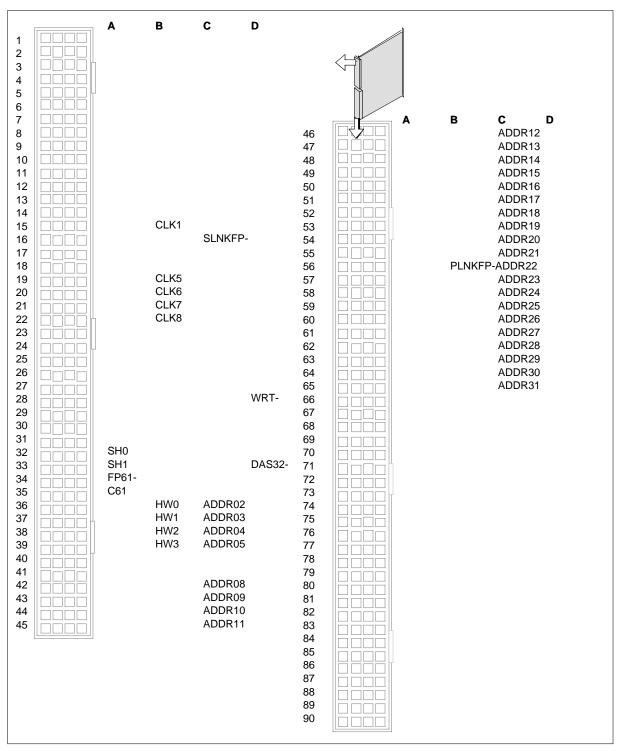

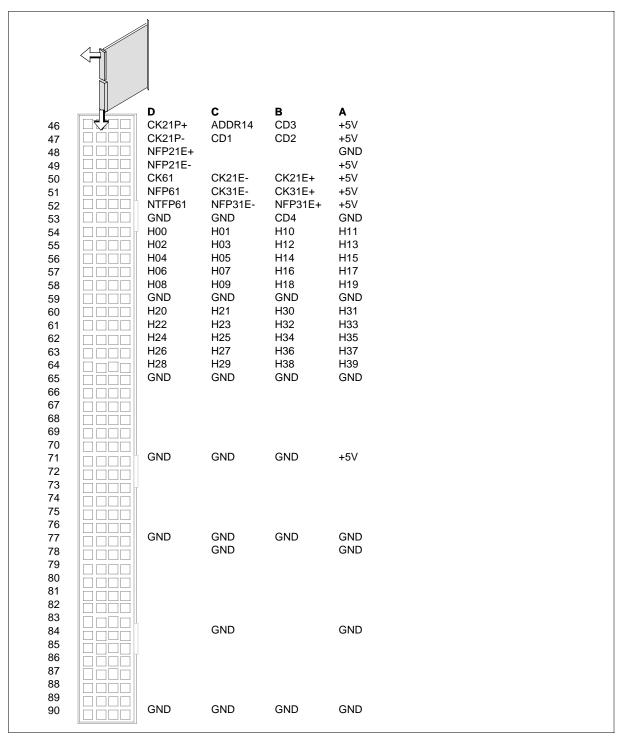

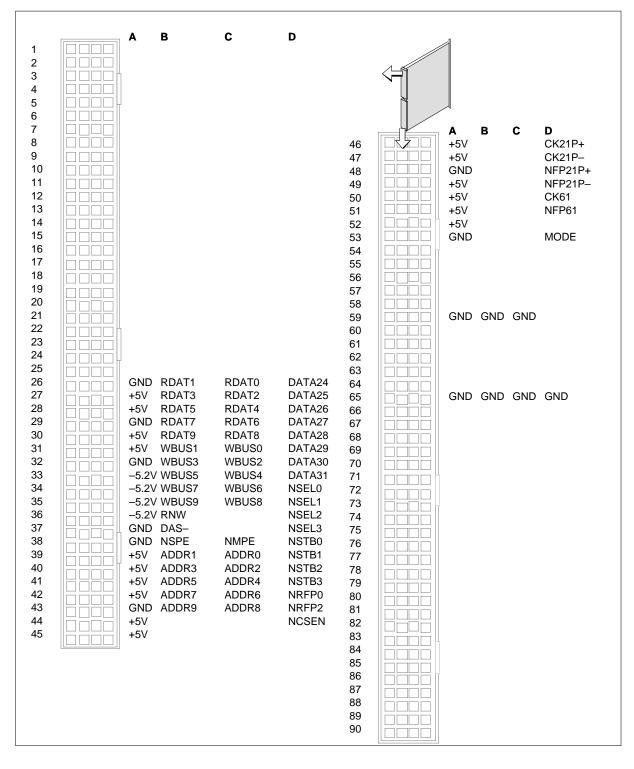

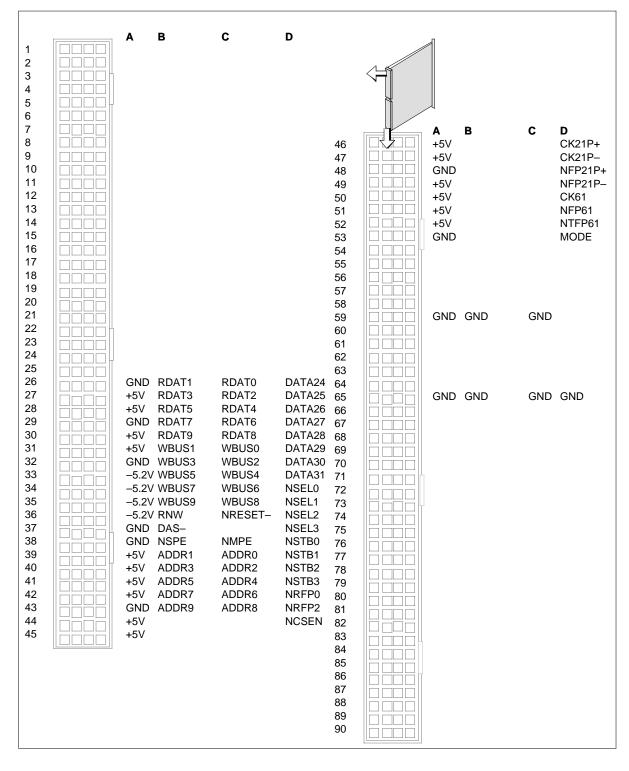

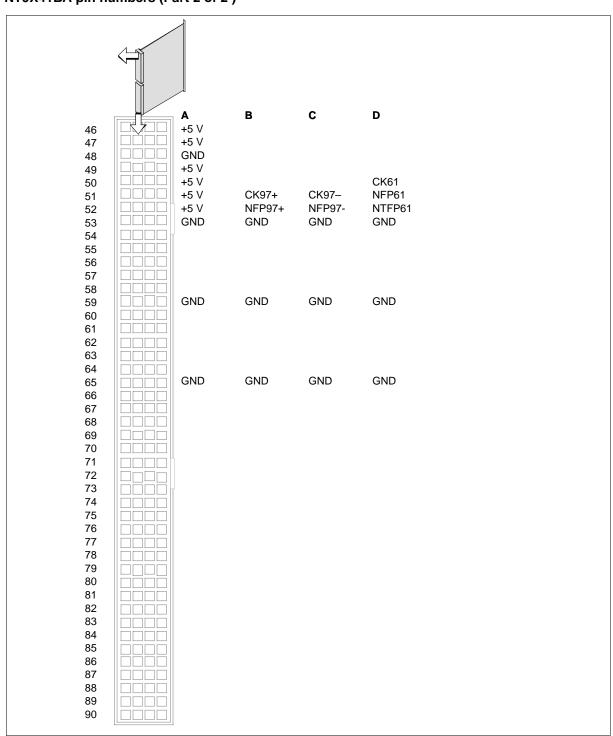

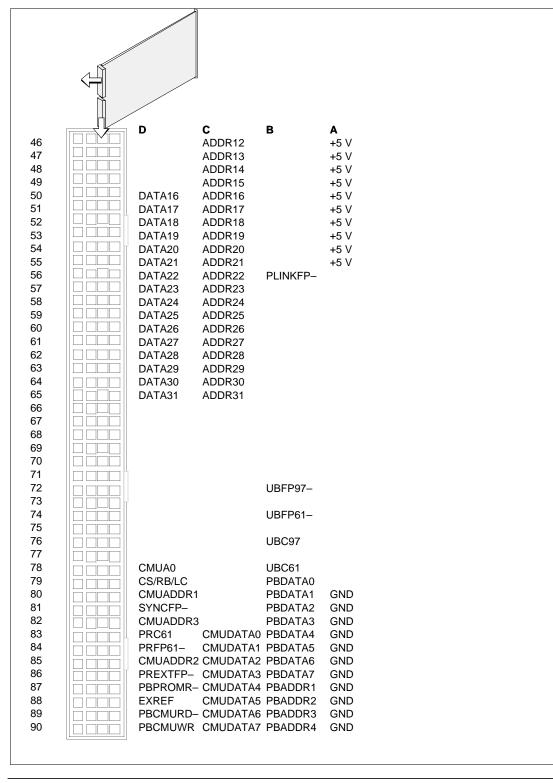

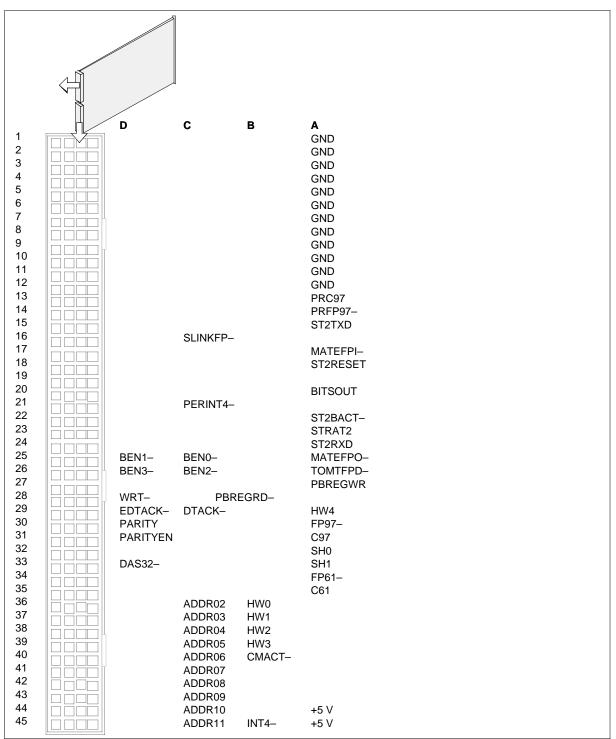

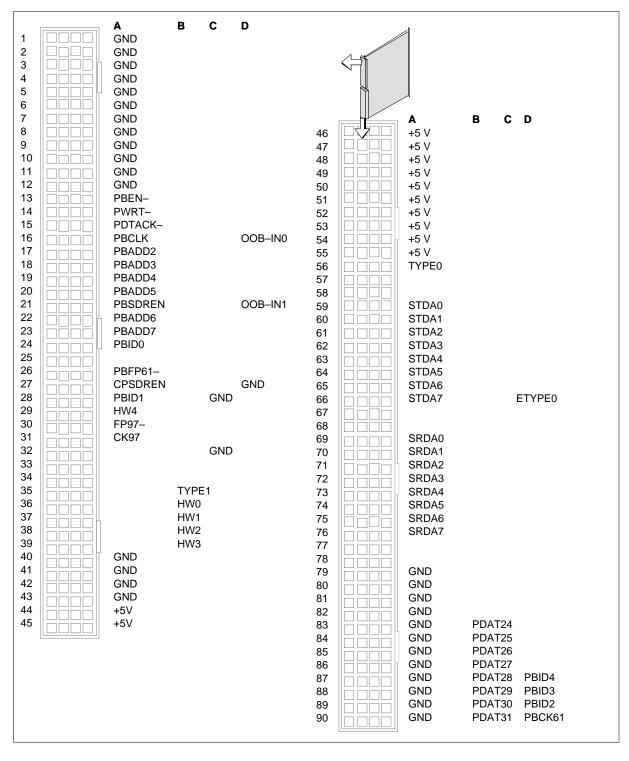

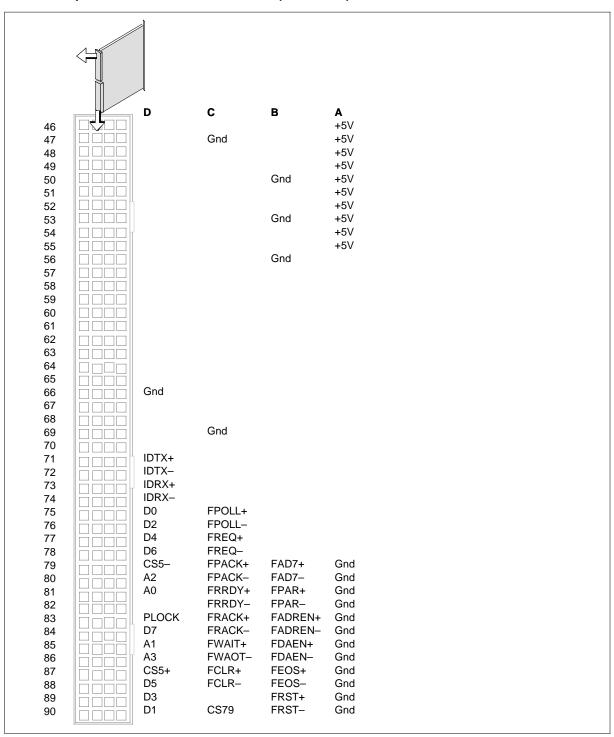

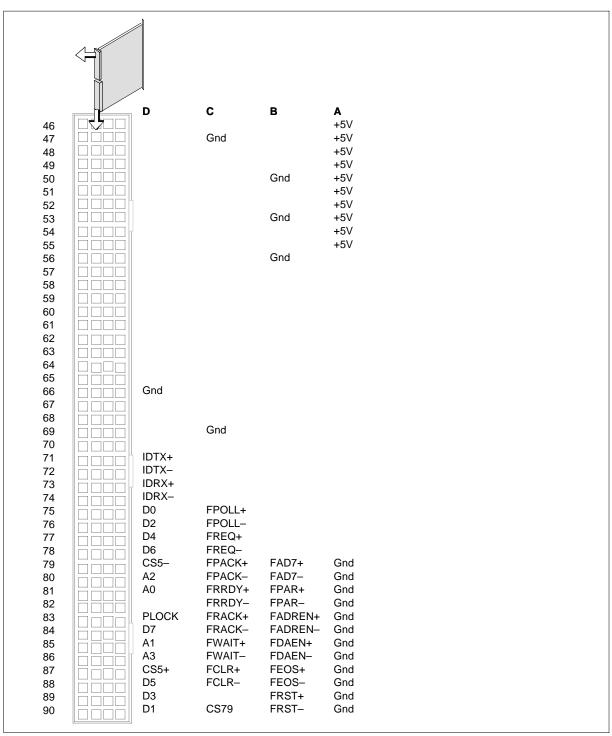

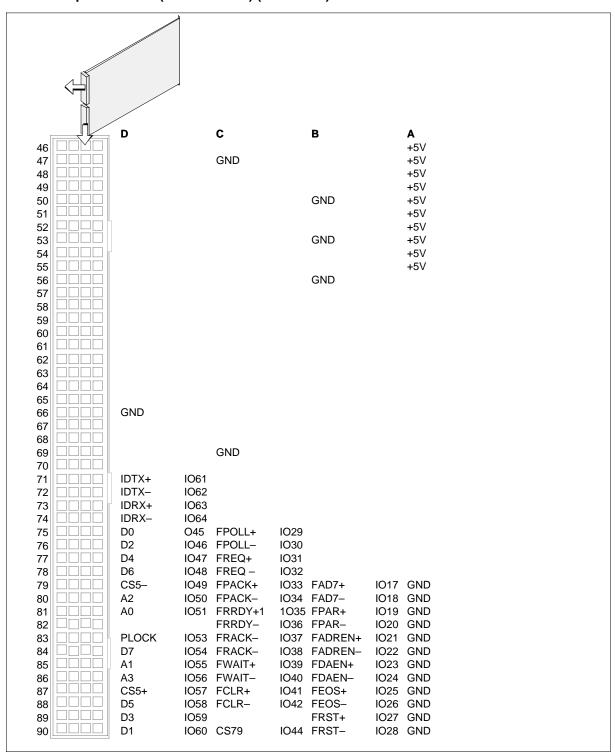

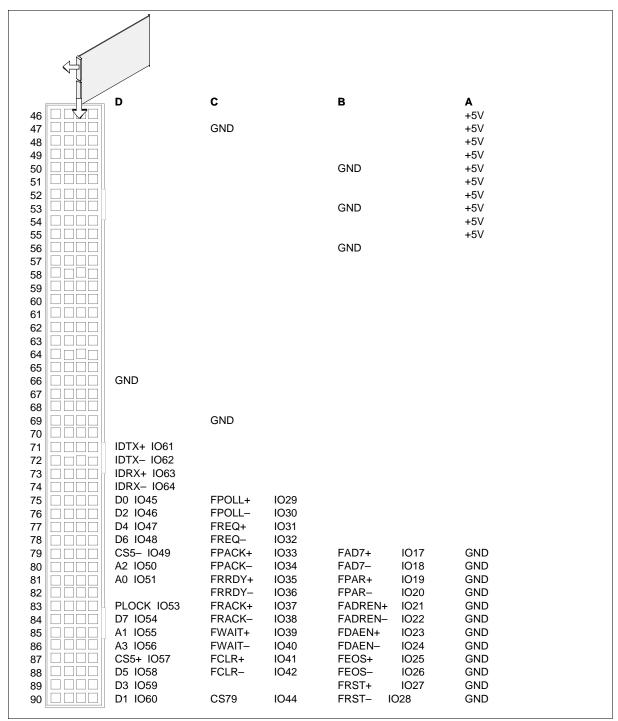

The pin numbers for the NT6X69DA appear in the following figure.

## NT6X69DA (end)

#### NT6X69DA pin numbers

|              | Α             | В            |                    | Ъ       |          |

|--------------|---------------|--------------|--------------------|---------|----------|

| 1A 1B        | GND           | GND          |                    |         |          |

| 2A 2B        | 5V            | 5V           | /                  |         |          |

| 3A 3B        | 5V            | 5V           |                    |         |          |

| 4A 4B        | 5V            | 5V           | ĸ                  |         |          |

| 5A 5B        | GND           | GND          |                    |         |          |

| 6A 6B        | FP-           | C97T         |                    |         |          |

| 7A 7B        | GND           | GND          | • U                |         |          |

| 8A 8B        | -ACT          |              | ĥ                  |         |          |

| 9A 9B        | C195TB*       |              |                    |         |          |

| 10A 10B      | CPROCS-*      |              |                    |         |          |

| 11A 11B      | GND           | GND          | ΥĽ                 | Α       | в        |

| 12A 12B      | DAS-          |              | 41A 41B            | GND     | GND      |

| 13A 13B      | LDS-          | С97-В        | 41A 41B<br>42A 42B |         | GND      |

| 14A 14B      | DTRACK-       | CPROCB       | 43A 43B            | ADDR12+ | D0*      |

| 15A 15B      | UDS-          | RUN*         | 43A 43B<br>44A 44B | ADDR13+ |          |

| 16A 16B      | WRT-          | TCEN-*       |                    | ADDR14+ | D1*      |

| 17A 17B      | IMCOUT**      | IMCIN**      | 45A 45B            | ADDR15+ | D2*      |

| 18A 18B      | GNDI          | NT4REQ**     | 46A 46B            | ADDR16+ | D3*      |

| 19A 19B      | GNDI          |              | 47A 47B            | ADDR17+ | D4*      |

| 20A 20B      |               |              | 48A 48B            | ADDR18+ | D5*      |

| 21A 21B      | PIN0          | POUT0        | 49A 49B            | ADDR19+ | D6*      |

| 22A 22B      | PIN1          | POUT1        | 50A 50B            | ADDR20+ | D7*      |

| 23A 23B      | PIN2          | POUT2        | 51A 51B            | ADDR21+ | DEOTVE   |

| 24A 24B      | PIN3          | POUT3        | 52A 52B            | SEN0    | DESTXT0- |

| 25A 25B      | PIN4          | POUT4        | 53A 53B            | SEN1    | DESTXT1- |

| 26A 26B      | PIN5          | POUT5        | 54A 54B            | SEN2    |          |

| 27A 27B      | PIN6          | POUT6        | 55A 55B            | PSPEN+  | SRCXTO-  |

| 28A 28B      | PIN7          | POUT7        | 56A 56B            | CSPEN+  | SRCXT1-  |

| 29A 29B      | ADDR01+       | F0017        | 57A 57B            | GND     | GND      |

| 30A 30B      | ADDR02+       |              | 58A 58B            | DATA00+ | SRC0*    |

| 31A 31B      | ADDR02+       |              | 59A 59B            | DATA01+ | SRC1*    |

| 32A 32B      | ADDR03+       |              | 60A 60B            | DATA02+ | SRC2*    |

| 33A 33B      | ADDR05+       |              | 61A 61B            | DATA03+ | SRC3*    |

| 34A 34B      | GND           | GND          | 62A 62B            | DATA04+ | SRC4*    |

| 35A 35B      | ADDR06+       | -FPM         | 63A 63B            | DATA05+ | SRC5*    |

| 36A 36B      | ADDR00+       | GND          | 64A 64B            | GND     | SRC6*    |

| 37A 37B      | ADDR08+       | C97M+        | 65A 65B            | DATA06+ | SRC7*    |

| 38A 38B      | ADDR00+       | GND          | 66A 66B            | DATA07+ | _        |

| 39A 39B      | ADDR03+       | CHOT         | 67A 67B            | CHOS    |          |

| 40A 40B      | ADDR10+       | СНОМ         | 68A 68B            | CHOR    | -        |

| 407 400      | ADDITT        | CHOM         | 69A 69B            | CHOS    |          |

|              |               |              | 70A 70B            | CHOR    | 1        |

|              |               |              | 71A 71B            |         |          |

| Notes:       |               |              | 72A 72B            |         |          |

|              | nnel signals  | no backplane | 73A 73B            |         |          |

| connection n |               |              | 74A 74B            | AUXR    |          |

|              |               |              | 75A 75B            | MODR    |          |

| 2 ** additio | nal signals o | n the NT6902 | 76A 76B            | GND     | GND      |

|              | on the NT690  |              | 77A 77B            |         |          |

| ,            |               |              | 78A 78B            | GND     | GND      |

|              |               |              | 79A 79B            |         |          |

|              |               |              | 80A 80B            | GND     | GND      |

|              |               |              |                    |         |          |

## NT6X69LA

## **Product description**

The NT6X69LA replaces any of the international variants of the NT6X69AB North American base pack. The NT6X69LA replaces the NT6X69BB (Turkey), the NT6X69DA (UK), the NT6X69FA (CEP), and the NT6X69KA (China). These variants differ only in the contents of the EPROM U20. The EPROM U20 holds the tone sets.

The NT6X69LA has 128 kbytes of RAM, with circuit support that replaces the 64 kbytes EPROM U20. This condition allows software to create and load tone sets.

The NT6X69LA has the ability to process message protocol and receive variable tone sets from the CC.

#### Location

The NT6X69LA is in slot 10.

## **Functional description**

#### **Functional blocks**

The NT6X69LA has the following functional blocks:

- network message (NM) interface

- parallel speech bus (SB) message interface

- SB connection memory

- intermodule connection (IMC) interface

- tone generator and tone RAM

- protocol processor (PP)

- facilities processor (FP) and PP shared memory

- shelf reset generator

- cyclic redundancy check (CRC) ROM

- process timing ROM

- FP interface

#### Network message interface

The channel 0 (CH0) signal from the active formatter tells data to leave and enter the shift registers. The CHO signal tells data to enter the NM interface serially. Data from the transmit hold register loads to the shift register before the CH0 time in every frame. After the CH0 time, data loads to the receive

holding register from the shift register. The PP can read from or write to the holding registers at any time but during CH0.

#### Parallel speech bus message interface

The synchronous PP in the SB interface transmits the message. The first half of the instruction cycle is for the PP. The PP writes to the transmit RAM or reads from the receive RAM. In the second half of the instruction cycle, the system puts data in the transmit holding register from the transmit RAM. This condition occurs according to the port/channel counter. Data writes to the receive RAM from the receive holding register.

#### Speech bus connection memory

The connection memory arbitrates the access of the different service cards to the SB on a time slot condition. The FP accesses the connection memory in the same way as the PP/FP shared memory. The PP cannot access the connection memory.

#### Intermodule connection interface

The IMC interface appears to the PP as a SB time slot. The FP assigns the time slot through the connection memory. The system exchanges data between the two shelves during the active CH0 time. The active clock gates the data exchange. Errors can occur with the IMC link when the two shelves are out of synchronization.

#### Tone generator and tone RAM

Tone generation circuits on the NT6X69LA card have the following:

- R09 tone generation chip

- tone RAM

- supporting circuits that provide for expansion of tone sample memory from 64 kbytes to 128 kbytes

- tone holding register

#### **Protocol processor**

The functional blocks that the protocol processor (PP) accesses appear below:

- 8K×8 RAM shared with the FP

- CRC ROM for CRC calculation the DMS-X protocol requires

- process timing ROM that allows the firmware to synchronize to the frame

- RSTGEN that allows the PP to initiate a shelf reset (MODRST) from the NT6X46 card (signaling processor memory plus card)

- INTGEN that allows the PP to initiate a level-four interrupt to the FP

- NM interface

- speech bus interface

- IMC interface

#### Facilities processor and protocol processor shared memory

The SP and PP communicate through an 8K×8 block of RAM that the two processors transparently share. This block serves as:

- a work space for the PP

- a buffer for messages the PP receives for the SP, and for messages the SP queues for the PP

- an opcode area that allows the SP to apply the interfaces indirectly

#### Shelf reset generator

The PP can initiate a shelf reset with the following sequence:

- the PP accesses the auxiliary reset strobe to clock the reset flip-flop

- the output of the reset flip–flop is driven to the backplane and connects to the NT6X46 card

- the NT6X46 card stops activity and issues the module reset signal to the rest of the shelf to acknowledge the reset

- the module reset that the NT6X46 card issues clears the reset flip-flop on the NT6X69 card

#### Cyclic redundancy check ROM

This ROM contains two tables used in a two-stage CRC accumulation process. To access the upper page, the PP can use the CRCL strobe that the CRCH strobe follows. To access the lower page, the PP only uses the CRCL strobe.

#### **Process timing ROM**

Process timing PROM allows the PP to synchronize each process time slot for the frame limit. The port/channel counter addresses the PROM. The PP can read the PROM during any instruction cycle.

#### Facilities processor interface

Address and control signals are buffered. An access sequence synchronizes FP requests and generates a read or write access cycle. This action occurs when a valid address falls in the range that the system assigns to this card type. The interface is asynchronous and an acknowledge signal indicates the end of the access cycle.

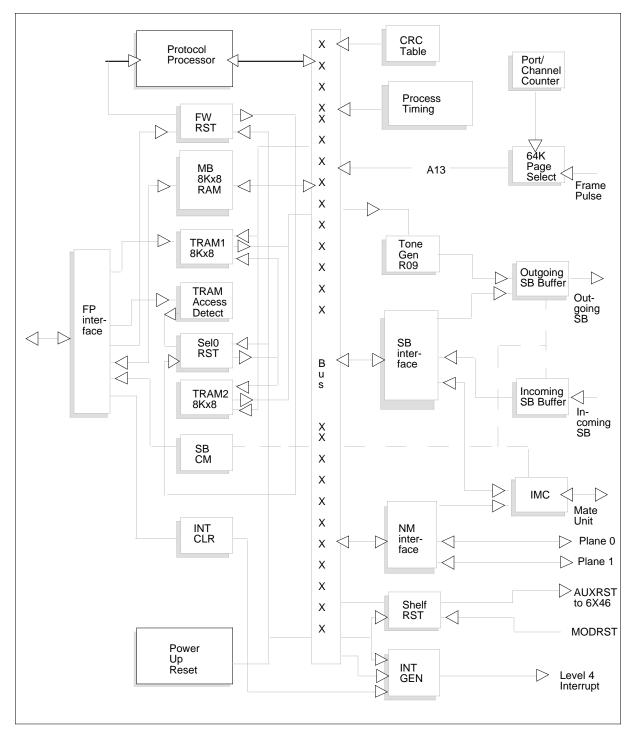

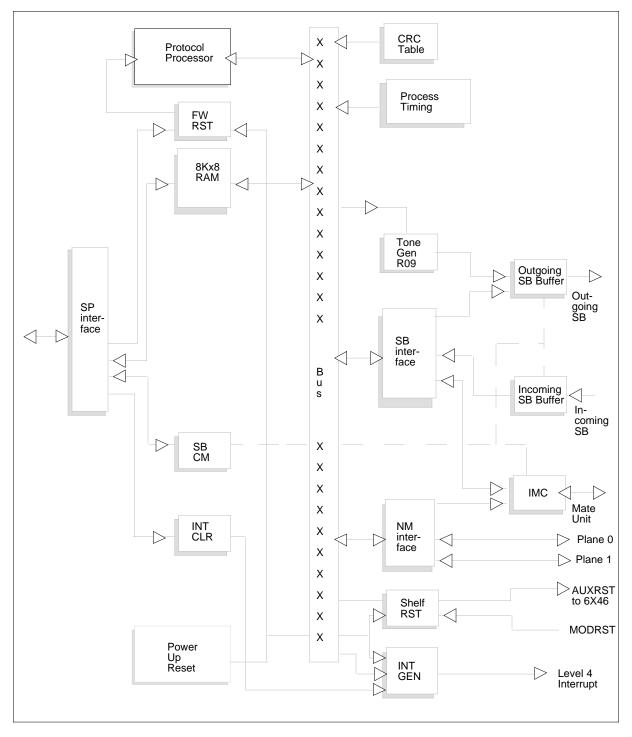

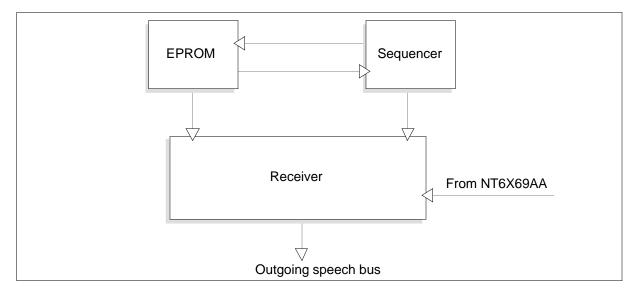

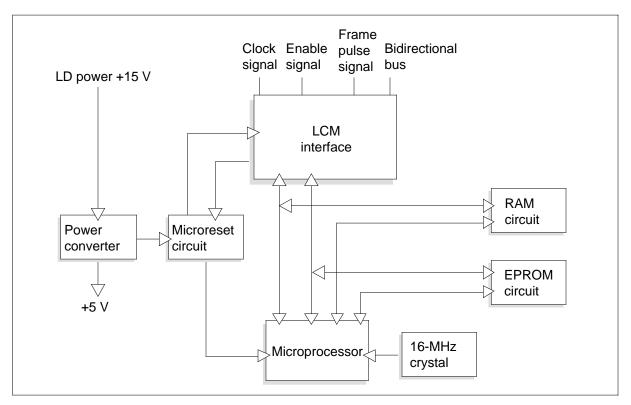

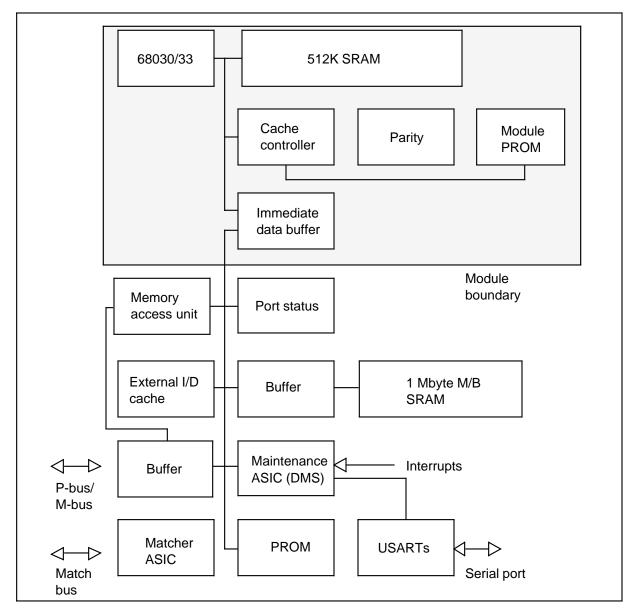

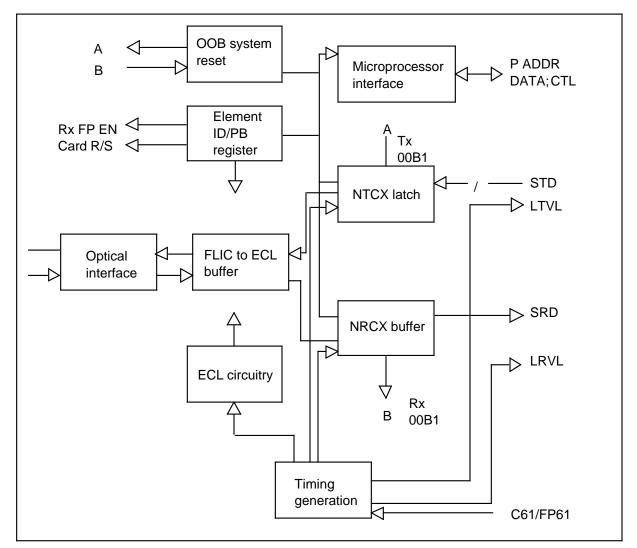

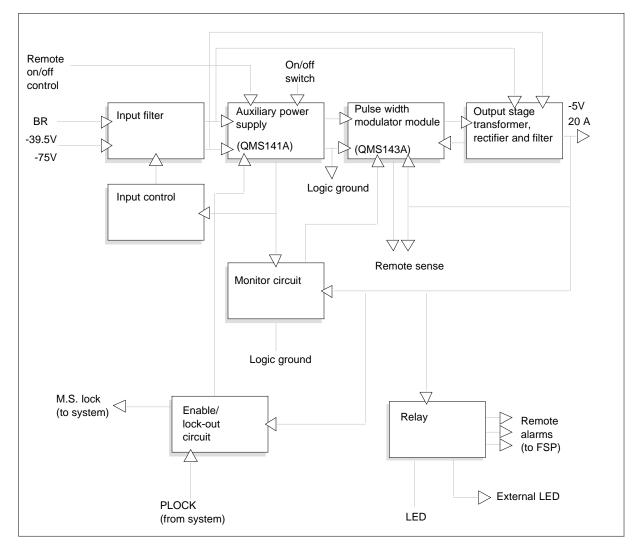

The relationship between the functional blocks appears in the following figure.

#### NT6X69LA functional blocks

## Signaling

## Pin numbers

The following figure shows the pin numbers for NT6X69LA.

*Note:* \* denotes test channel signals, no backplane connection needed. \*\* denotes additional signals on the 6902 card but not on the 6901. \*\*\* denotes temporary signals that the NT6X79 card requires.

#### NT6X69LA pin numbers

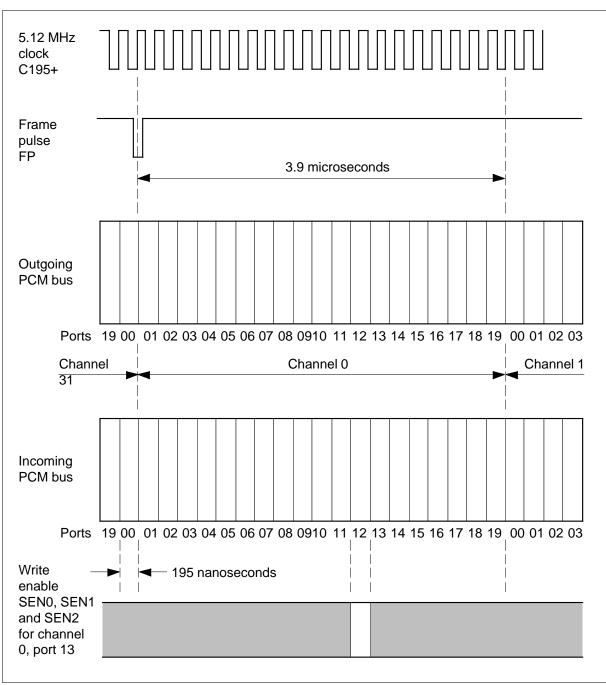

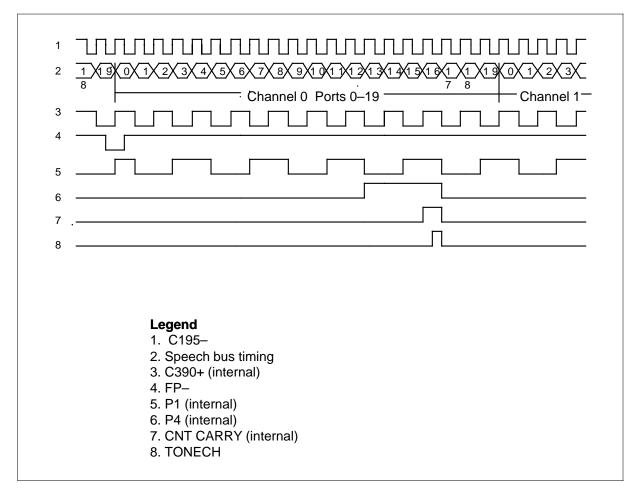

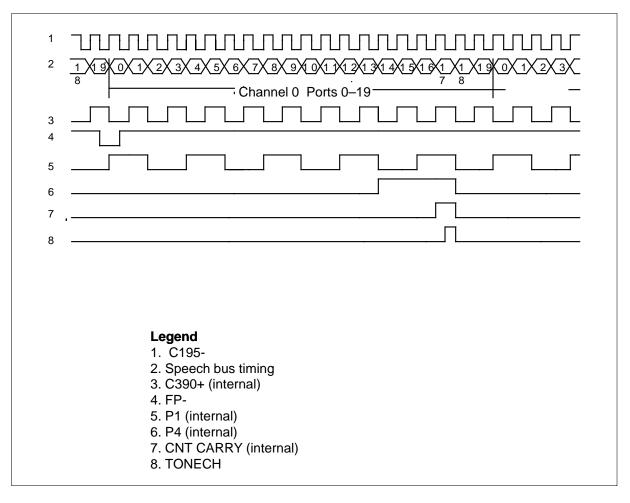

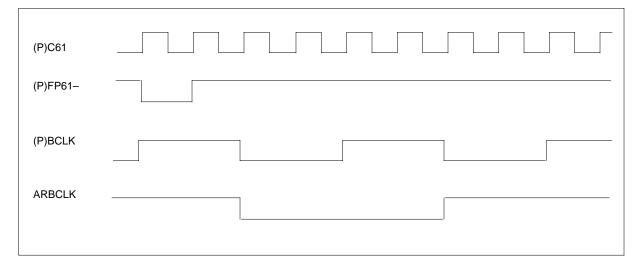

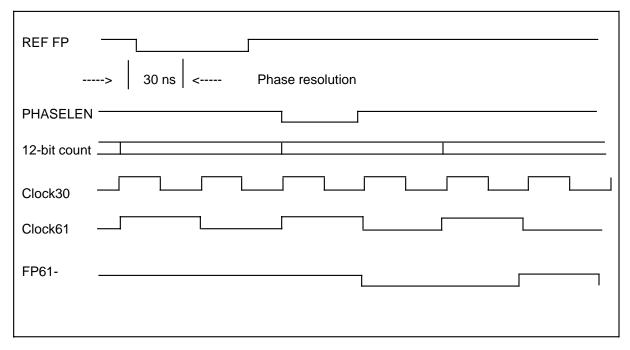

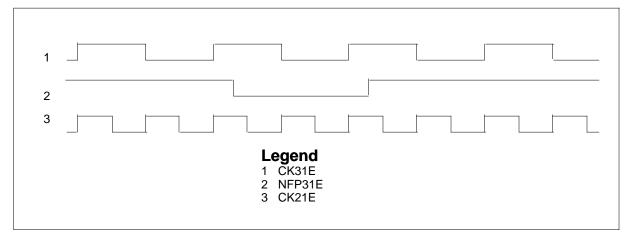

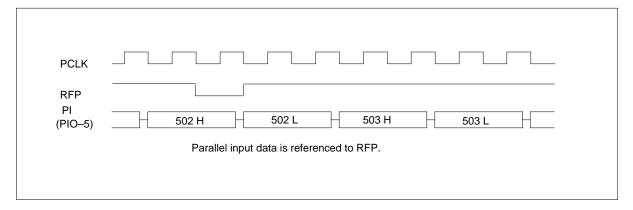

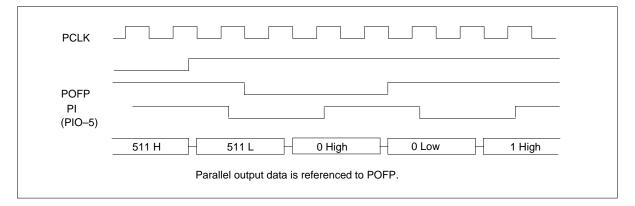

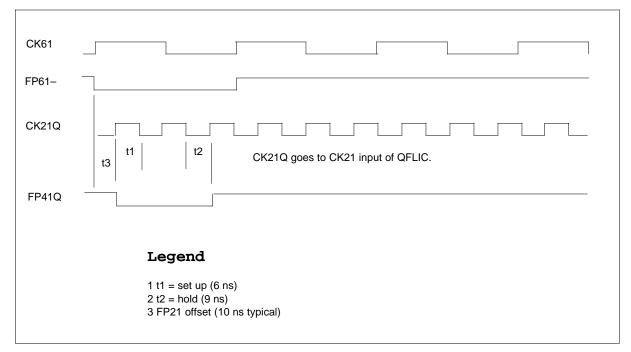

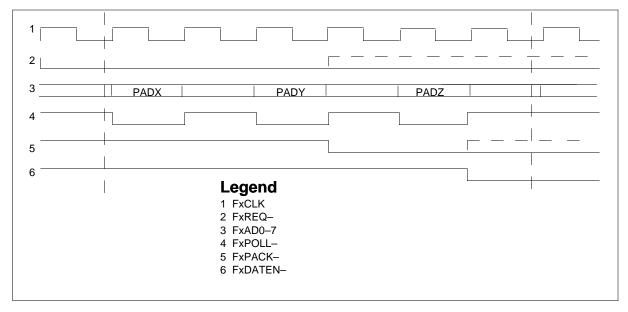

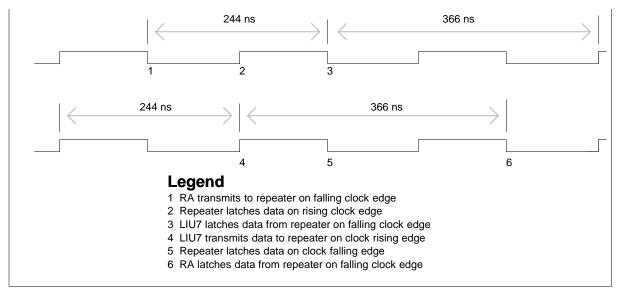

#### Timing

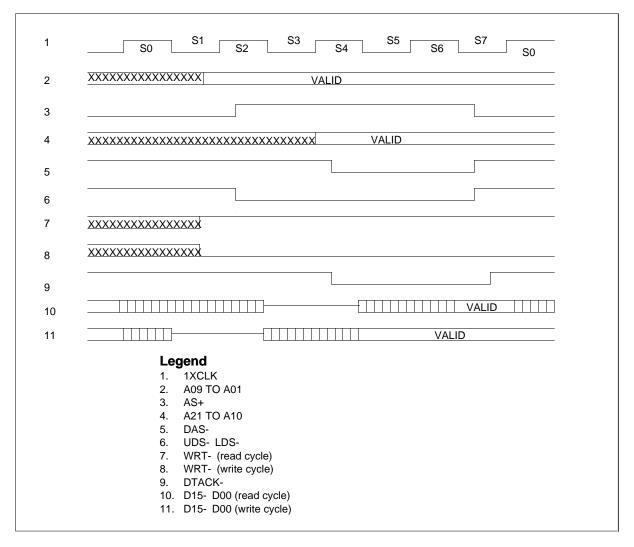

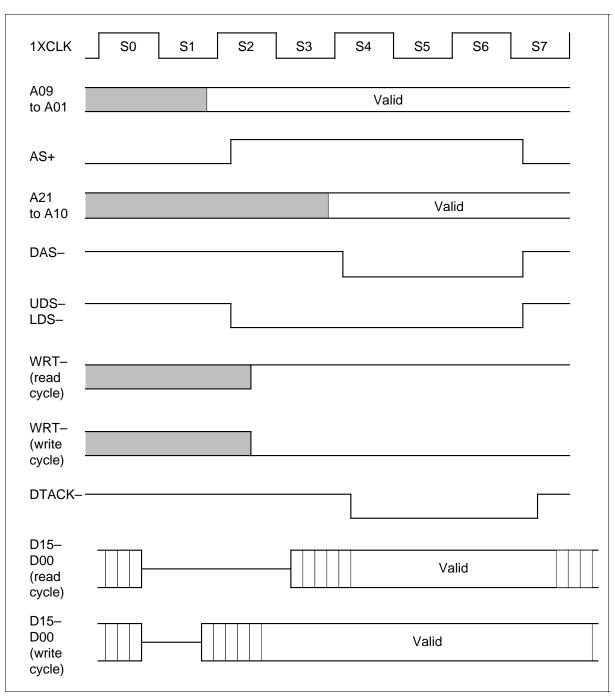

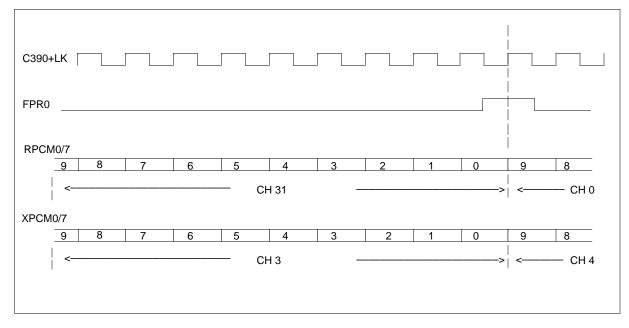

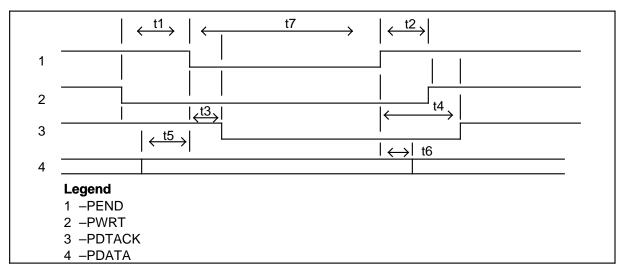

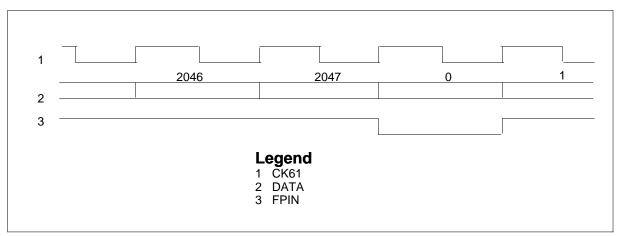

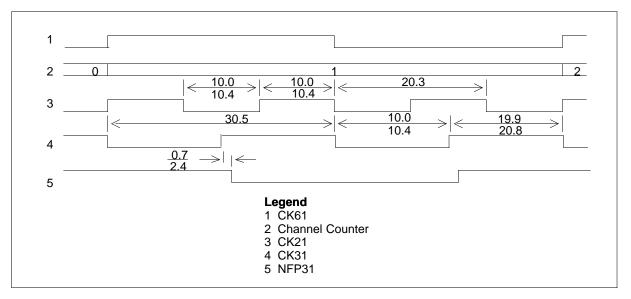

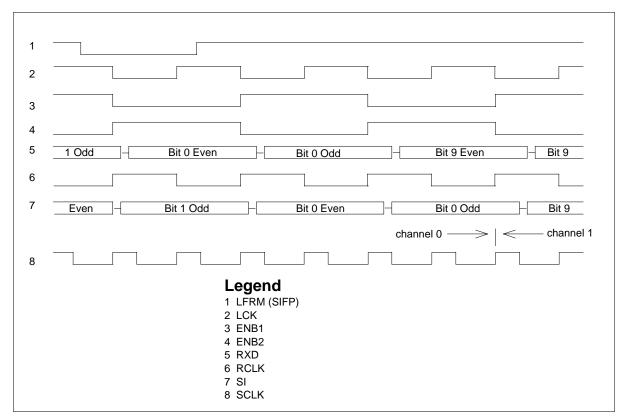

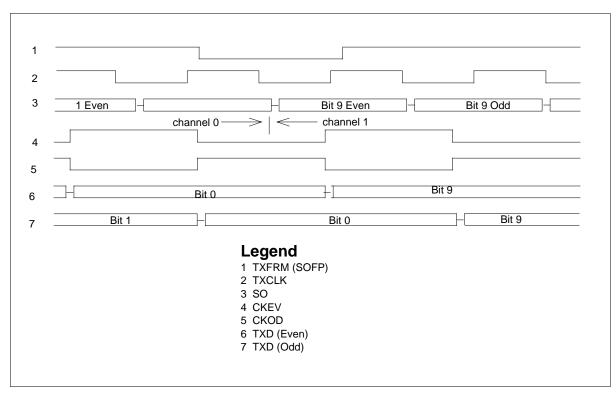

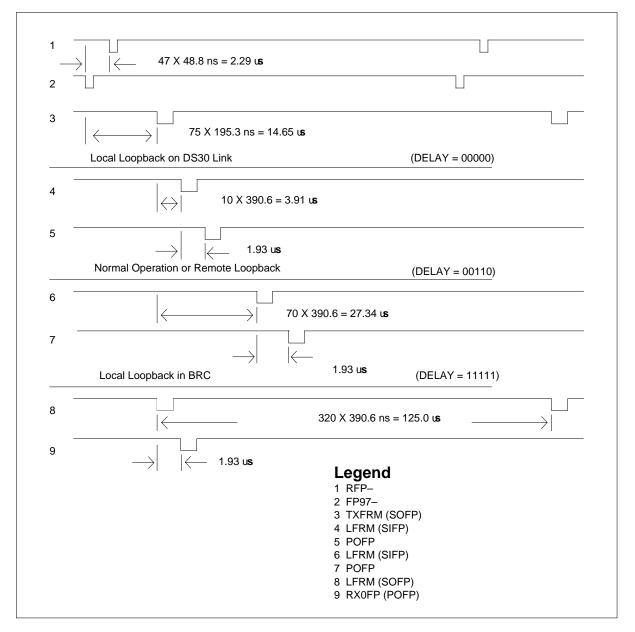

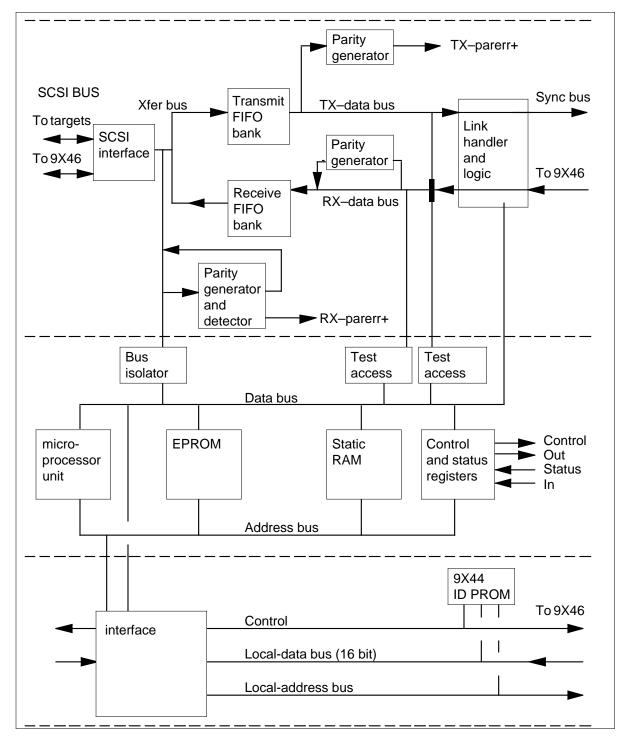

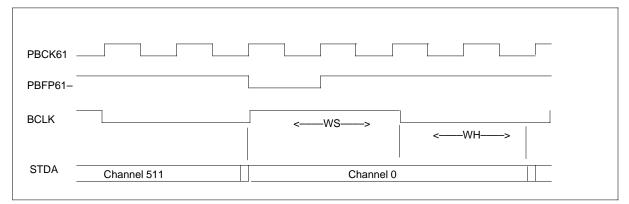

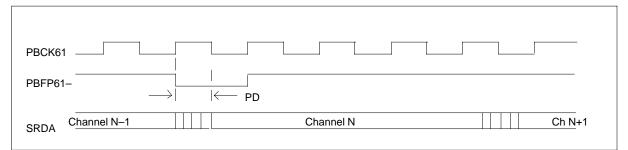

The timing for the NT6X69LA appear in the following figures.

| С97                   |   |

|-----------------------|---|

| C195F                 |   |

| PROCYC+               |   |

| DS (U98P11)           | ] |

| DAS-                  |   |

| ADRM (U115P9)         | 1 |

| DTACK-                |   |

| WRT-<br>Scale:<br>195 |   |

#### NT6X69LA A-bus interface timing: FP read cycle

| C195F         |  |

|---------------|--|

| PROCYC+       |  |

| WRT-          |  |

| ENMBOUT-      |  |

| ENCMOUT-      |  |

| DTACK-        |  |

| Scale:<br>195 |  |

## NT6X69LA (end)

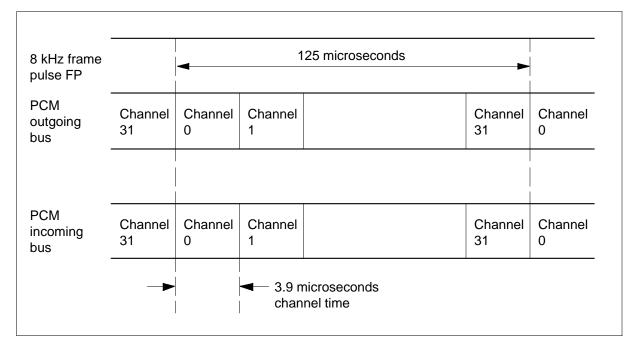

#### NT6X69LA network module interface timing

## NT6X69LB

#### **Product description**

The system uses the NT6X69LB CPP message protocol and downloadable tones card. This card replaces any of the international variants of the NT6X69AB North American base pack. These variants are the NT6X69BB (Turkey), the NT6X69DA (UK), the NT6X69FA (CEP), and the NT6X69KA (China). These variants differ only in the contents of the EPROM U20. The EPROM U20 holds the tone sets.

The NT6X69LB has 128 kbytes of RAM with supporting circuits that replace the 64 kbyte EPROM U20. This RAM allows software to create and load tone sets.

The NT6X69LB processes message protocol and receives variable tone sets from the central control (CC).

#### Location

The NT6X69LB is in slot 10.

## **Functional description**

#### Functional blocks

The NT6X69LB contains the following functional blocks:

- network message (NM) interface

- parallel speech bus (SB) message interface

- SB connection memory

- inter-module connection (IMC) interface

- interrupt generator

- tone generator and tone RAM

- protocol processor (PP)

- facilities processor (FP) and PP shared memory

- shelf reset generator

- cyclic redundancy check (CRC) ROM

- process timing ROM

- FP interface

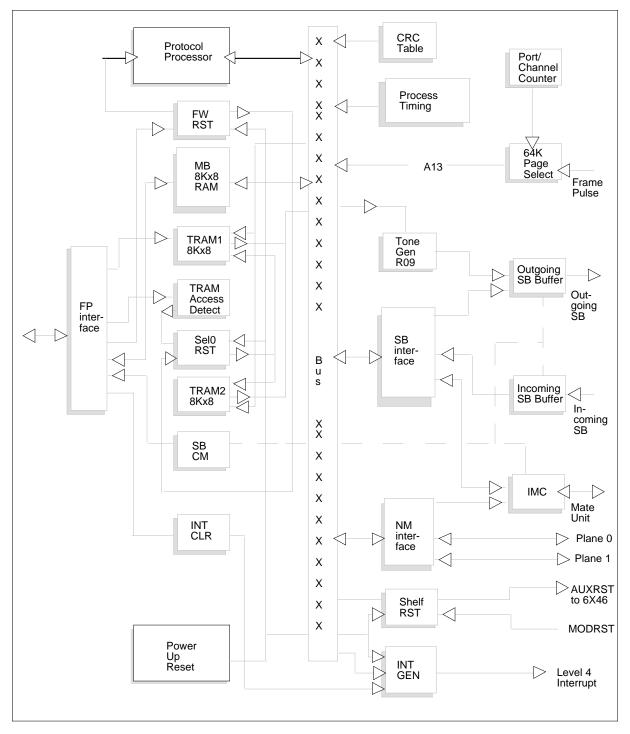

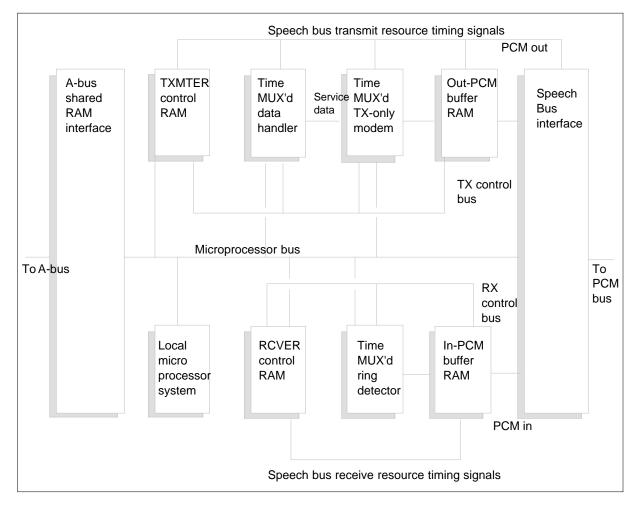

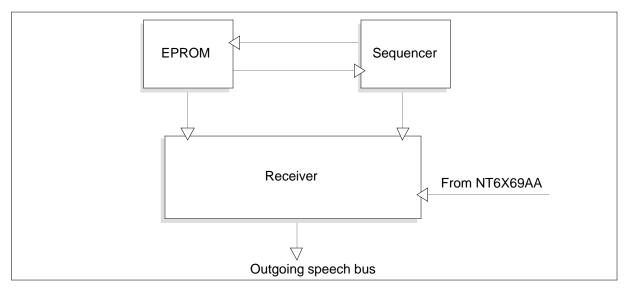

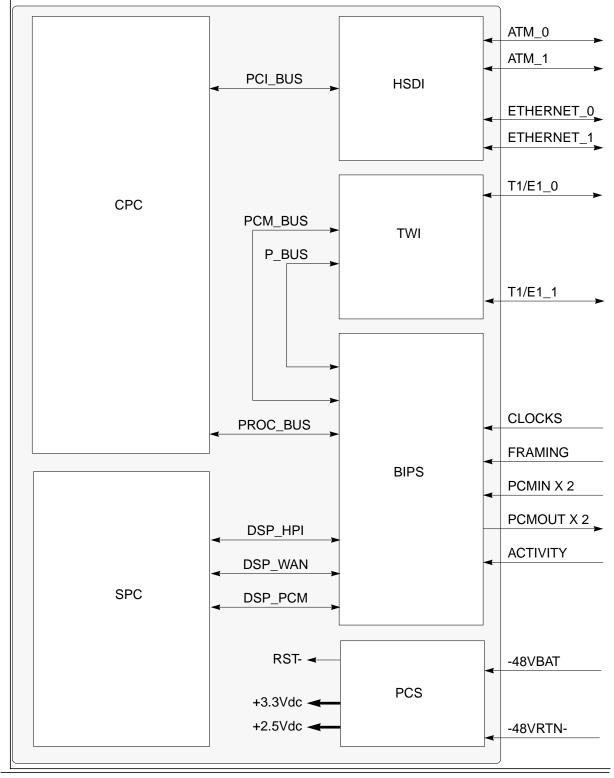

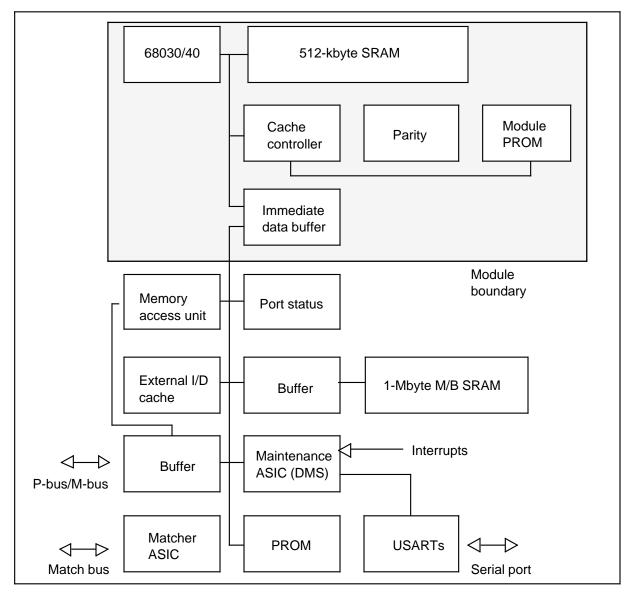

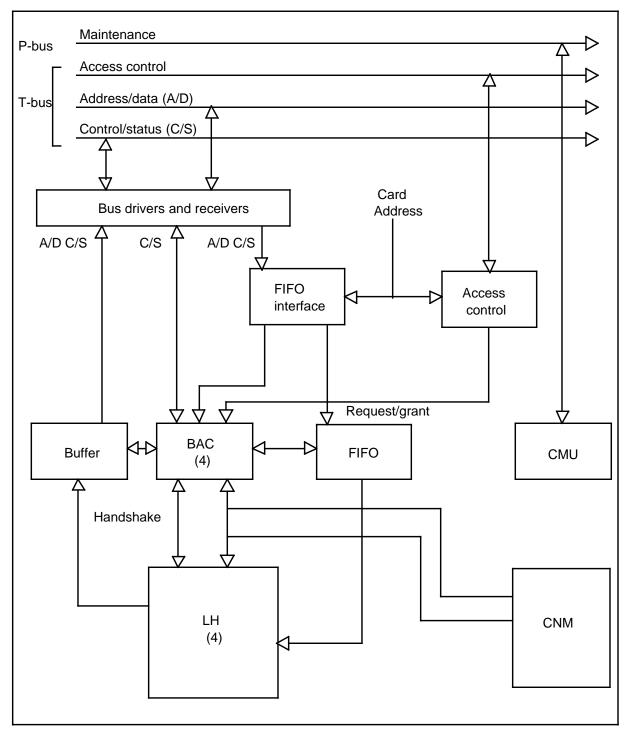

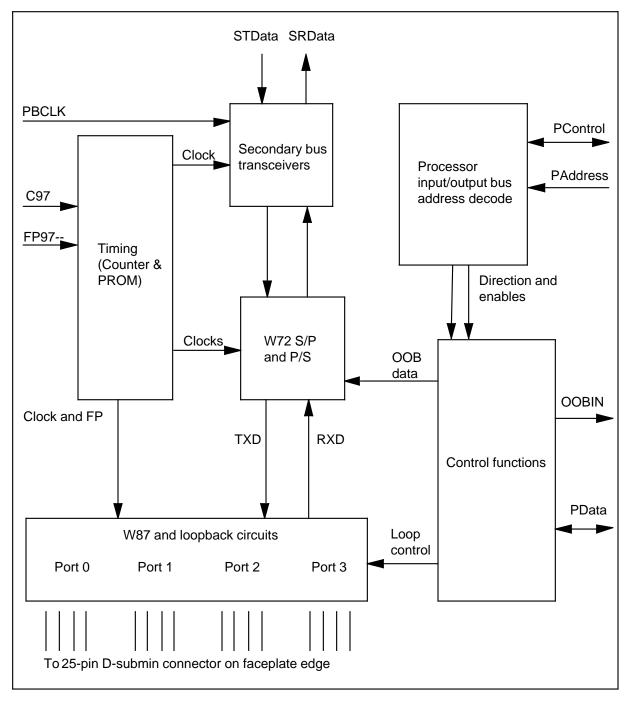

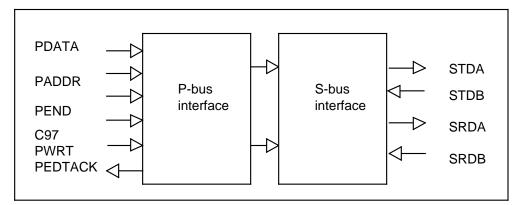

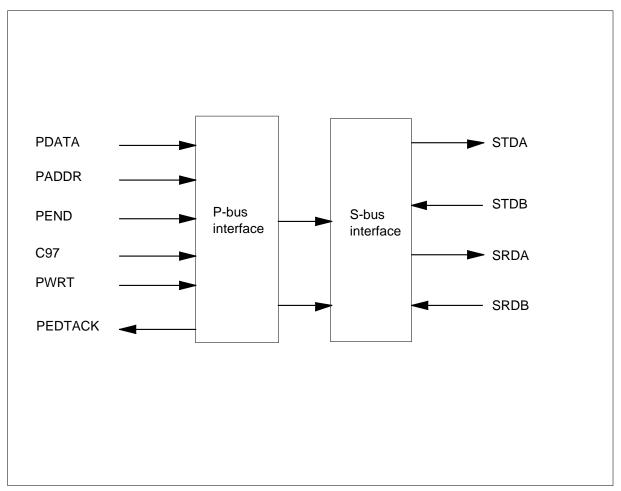

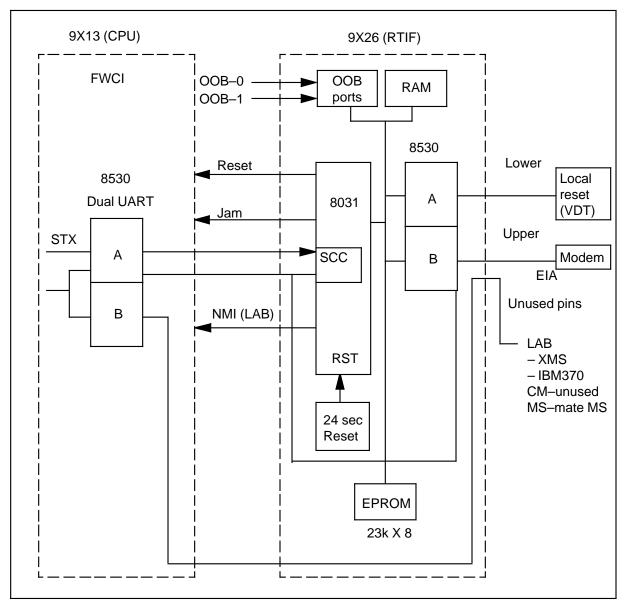

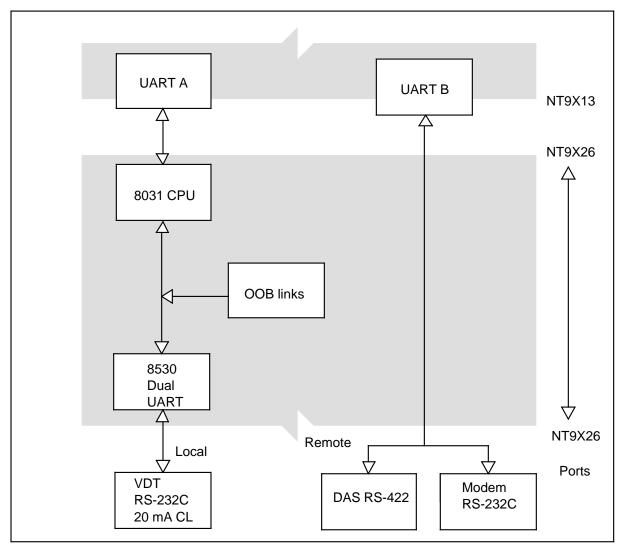

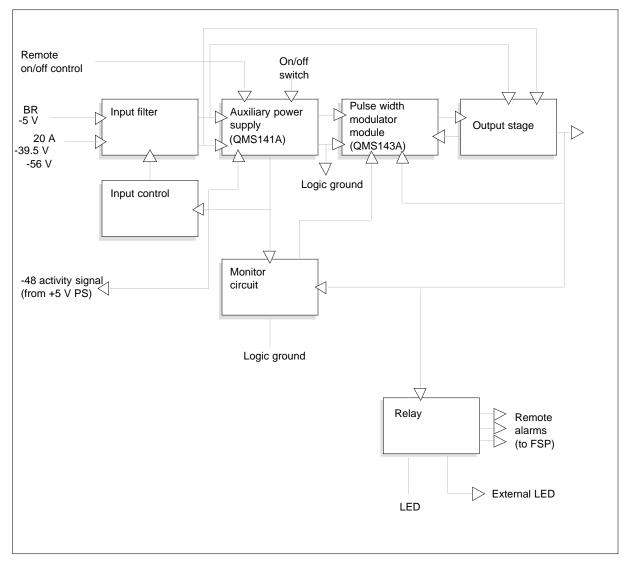

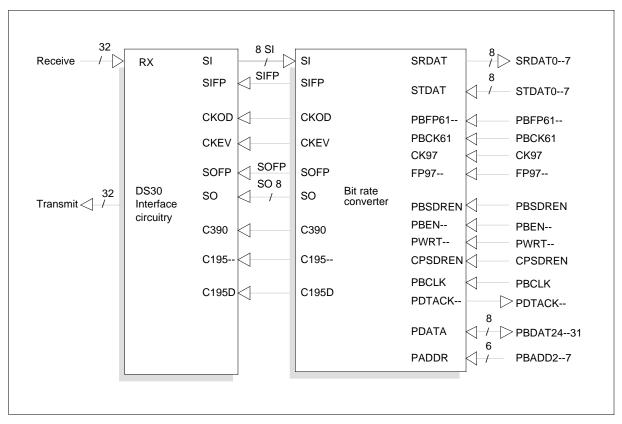

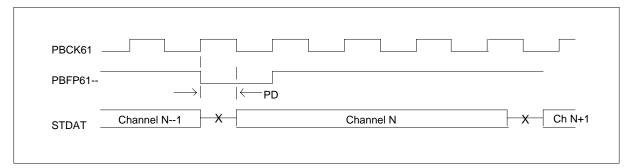

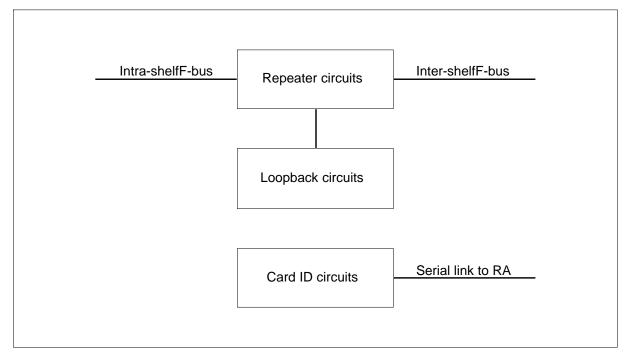

The relationship between the functional blocks appears in the following figure.

#### NT6X69LB functional blocks

#### Network message interface

The channel 0 (CH0) signal from the active formatter tells data to leave and enter the NM interface shift registers serially. Data from the transmit hold register loads to the shift register in every frame before the CH0 time. Data from the shift register loads into the receive holding register in every frame after the CH0 time. The PP can read from or write to the holding registers at any time other than CH0.

#### Parallel speech bus message interface

The synchronous PP in the SB interface sends out the message. The first half of the instruction cycle is for the PP. This part is for the PP to write to the transmit RAM or to read from the receive RAM. In the second half of the instruction cycle, data is put in the transmit holding register. The port and channel counter determines how the data is put in the transmit holding register from the transmit RAM. The receive holding register writes data to the receive RAM.

#### Speech bus connection memory

The connection memory controls access of the different service cards to the SB on a time–slot condition. The FP accesses the connection memory in the same way as the PP/FP shared memory. The PP cannot access the connection memory.

#### Inter-module connection interface

The IMC interface appears to the PP as an SB time slot. The FP assigns the time slot through the connection memory. The system exchanges data between the two shelves during the active CH0 time. The active clock gates the data exchange. Errors can occur with the IMC link when the two shelves are out of synchronization.

#### Tone generator and tone RAM

Tone generation circuits on the NT6X69LB card have the following:

- R09

- tone generation chip

- tone RAM

- supporting circuits, to provide for expansion of tone sample memory from 64 kbyte to 128 kbyte

- tone holding register

#### **Protocol processor**

The PP accesses the following functional blocks:

- 8-kbyte-by-8 RAM shared with the FP

- CRC ROM for CRC calculation the DMS-X protocol requires

- process timing ROM that allows the firmware to synchronize to the frame

- RSTGEN that allows the PP to initiate a shelf reset (MODRST) from the NT6X46 card

- INTGEN that allows the PP to initiate a level-four interrupt to the FP

- NM interface

- speech bus interface

- IMC interface

#### Facilities processor and protocol processor shared memory

The FP and PP communicate through an 8–kbyte–by–8 block of RAM that the two processors transparently share.

This block serves several functions:

- a work space for the PP

- a buffer for messages the PP receives for the FP and for messages the FP queues for the PP

- an opcode area that allows the FP to access the interfaces indirectly

#### Shelf reset generator

The PP can initiate a shelf reset with the following sequence:

- 1. The PP accesses the auxiliary reset strobe to clock the reset flip–flop.

- 2. The output of the reset flip–flop is driven to the backplane and connects to the NT6X46 card.

- 3. The NT6X46 card gives up activity and issues the module reset signal to the rest of the shelf to acknowledge the reset.

- 4. The module reset that the NT6X46 card issues clears the reset flip–flop on the NT6X69 card.

#### Cyclic redundancy ROM

A two-stage CRC accumulation process uses the two tables in this ROM. To access the upper page, the PP can use the CRCL strobe followed by the CRCH strobe. To access the lower page, the PP uses the CRCL strobe only.

#### **Process timing ROM**

Process timing PROM allows the PP to synchronize each process time slot according to the frame limit. The port and channel counter addresses the PROM. The PP can read the PROM during any instruction cycle.

#### Facilities processor interface

Address and control signals are buffered. An access sequence synchronizes FP requests and generates a read or write access cycle. This action occurs when a valid address falls in the range that the system assigns to this card type. The interface is asynchronous and an acknowledge signal indicates the end of the access cycle.

## Signaling

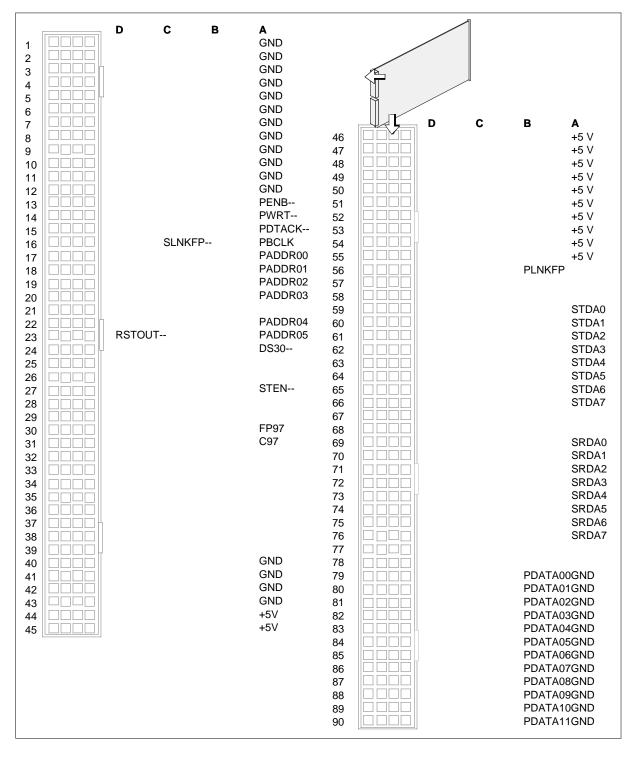

#### **Pin numbers**

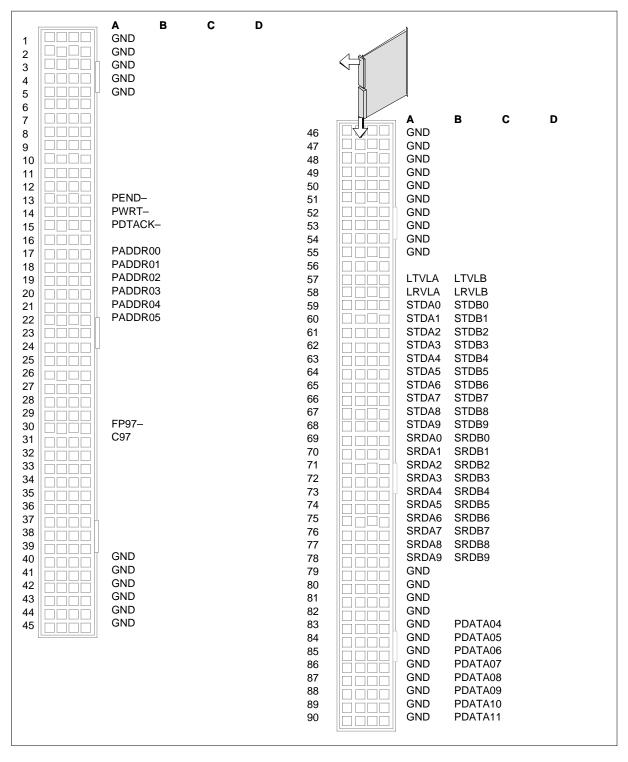

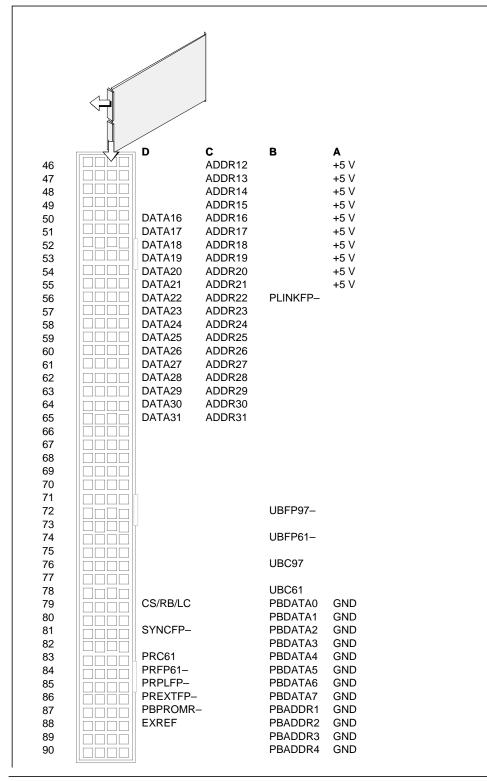

The pin numbers for NT6X69LB appear in the following figure.

#### NT6X69LB pin numbers

| Г  | 1    | Α              | В                           |    |          |         |           |

|----|------|----------------|-----------------------------|----|----------|---------|-----------|

| 1  |      | GND            | GND                         |    |          |         |           |

| 2  |      | 5V             | 5V                          |    | 1-15     |         |           |

| 3  | IFF! | 5V             | 5V                          | •  |          |         |           |

|    |      | 5V<br>5V       | 5V<br>5V                    |    |          |         |           |

| 4  |      |                |                             |    | 1¥       |         |           |

| 5  |      | GND            | GND                         |    |          |         |           |

| 6  |      | FP–            | С97Т                        |    |          | •       | 8         |

| 7  |      | GND            | GND                         | 44 | r¥=      | A       | B         |

| 8  |      | -ACT           |                             | 41 |          | GND     | GND       |

| 9  |      | C195TB*        |                             | 42 |          | ADDR12+ |           |

| 10 |      | CPROCS-*       |                             | 43 |          | ADDR13+ | D0*       |

| 11 |      | GND            | GND                         | 44 |          | ADDR14+ | D1*       |

| 12 |      | DAS-           |                             | 45 |          | ADDR15+ | D2*       |

| 13 |      | LDS-           | С97–В                       | 46 |          | ADDR16+ | D3*       |

| 14 |      | DTACK-         | CPROCB                      | 47 |          | ADDR17+ | D4*       |

| 15 |      | UDS-           | RUN*                        | 48 |          | ADDR18+ | D5*       |

|    |      |                |                             | 49 |          | ADDR19+ | D6*       |

| 16 |      | WRT-           | TCEN-*                      | 50 |          | ADDR20+ | D7*       |

| 17 | 님님   | IMCOUT**       |                             | 51 |          | ADDR21+ |           |

| 18 |      | GND            | INT4REQ**                   | 52 |          | SEN0    | DESTXT0-  |

| 19 |      |                |                             | 53 |          | SEN1    | DESTXT1-  |

| 20 |      |                |                             | 54 |          |         | DESTATI-  |

| 21 |      | PIN0           | POUT0                       |    |          | SEN2    |           |

| 22 |      | PIN1           | POUT1                       | 55 |          | PSPEN+  | SRCXT0-   |

| 23 |      | PIN2           | POUT2                       | 56 |          | CSPEN+  | SRCXT1-   |

| 24 |      | PIN3           | POUT3                       | 57 |          | GND     | GND       |

| 25 |      | PIN4           | POUT4                       | 58 |          | DATA00+ | SRC0*     |

| 26 |      | PIN5           | POUT5                       | 59 |          | DATA01+ | SRC1*     |

| 27 |      | PIN6           | POUT6                       | 60 |          | DATA02+ | SRC2*     |

| 28 |      | PIN7           | POUT7                       | 61 |          | DATA03+ | SRC3*     |

| 29 |      | ADDR01+        |                             | 62 |          | DATA04+ | SRC4*     |

| 30 |      | ADDR02+        |                             | 63 |          | DATA05+ | SRC5*     |

| 31 |      | ADDR03+        |                             | 64 |          | GND     | SRC6*     |

| 32 |      | ADDR04+        |                             | 65 |          | DATA06+ | SRC7*     |

| 33 |      | ADDR05+        |                             | 66 |          | DATA07+ |           |

|    |      |                | CND                         | 67 |          |         | CH0S0     |

| 34 |      | GND            | GND                         | 68 |          |         | CH0R0     |

| 35 |      | ADDR06+        | -FPM                        | 69 |          |         | CH0S1     |

| 36 |      | ADDR07+        | GND                         | 70 |          |         | CHOR1     |

| 37 | 니브브리 | ADDR08+        | C97M+                       | 71 |          |         | (T1***)   |

| 38 |      | ADDR09+        | GND                         | 72 |          |         |           |

| 39 |      | ADDR10+        | CH0T                        |    |          |         | (T2***)   |

| 40 |      | ADDR11+        | CH0M                        | 73 |          |         | T3***)    |

| L  |      |                |                             | 74 |          |         | AUXRST-** |

|    |      |                |                             | 75 |          |         | MODRST-** |

|    |      | * = test char  | nnel signals, no backplane  | 76 |          | GND     | GND       |

|    |      | connection ne  |                             | 77 |          |         |           |

|    |      |                | al signals on the 6902 card | 78 |          | GND     | GND       |

|    |      | but not on th  | •                           | 79 |          |         |           |

|    |      |                | orary signals that the      | 80 |          | GND     | GND       |

|    |      | NT6X79 card    |                             |    | <u> </u> |         |           |

|    |      | INI UNI 3 Udlu | roquiros.                   |    |          |         |           |

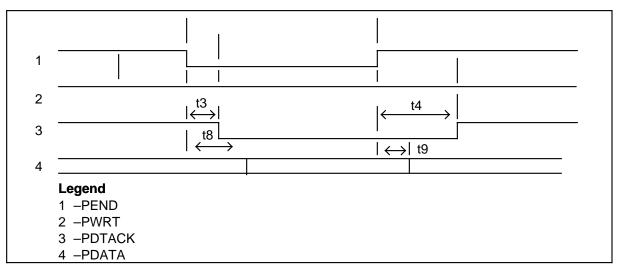

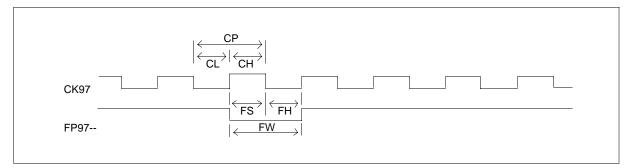

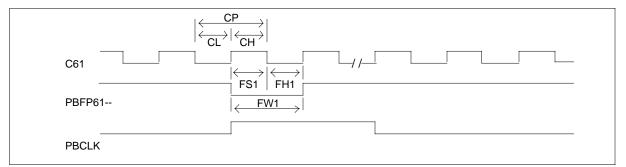

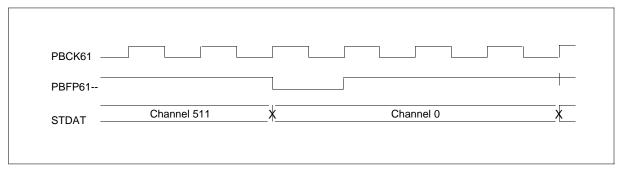

#### Timing

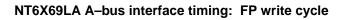

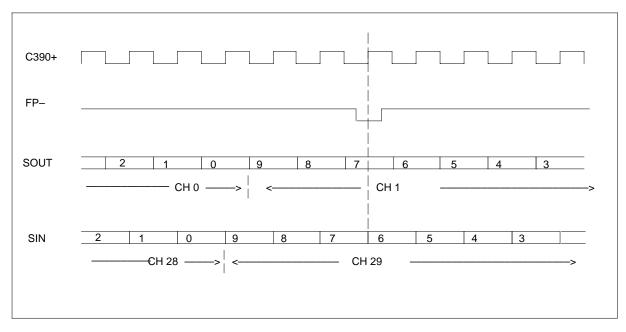

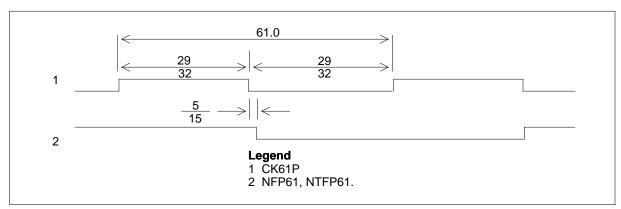

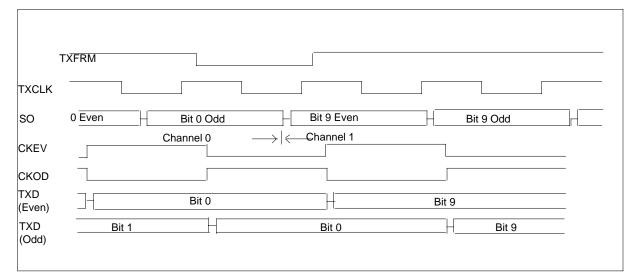

The timing for the NT6X69LB appears in the following figures.

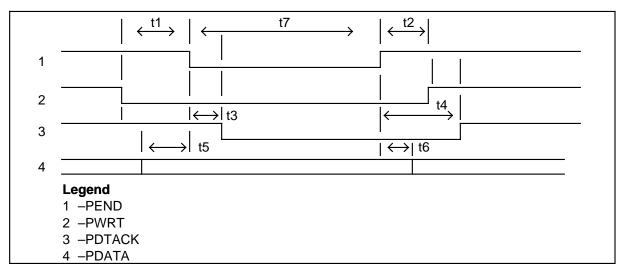

#### NT6X69LB A-bus interface timing: FP write cycle

| C97           |          |

|---------------|----------|

| C195F         |          |

| PROCYC+       |          |

| DS (U98P11)   |          |

| DAS-          |          |

| ADRM (U115P9) | ]        |

| DTACK-        |          |

| WRT-          |          |

| Scale:        | <b> </b> |

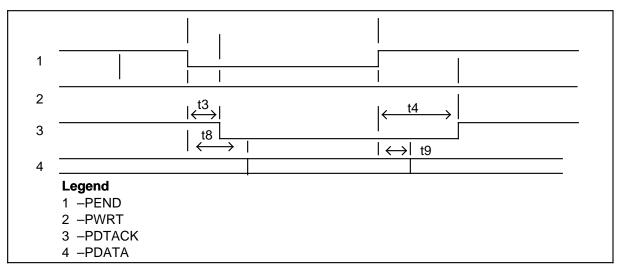

#### NT6X69LB A-bus interface timing: FP read cycle

| C195F             |  |

|-------------------|--|

| PROCYC+           |  |

| WRT-              |  |

| ENMBOUT-          |  |

| ENCMO <u>UT</u> - |  |

| DTACK-            |  |

| Scale:            |  |

## NT6X69LB (end)

#### NT6X69LB network module interface timing

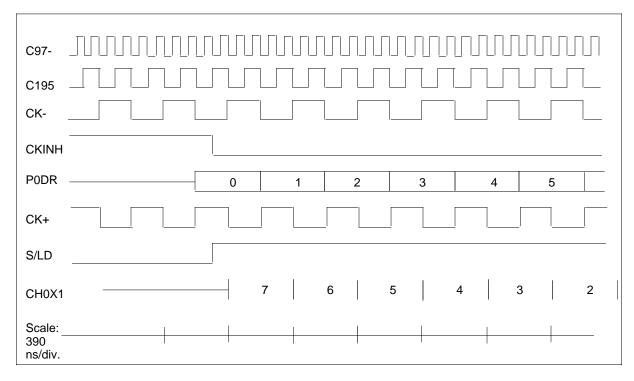

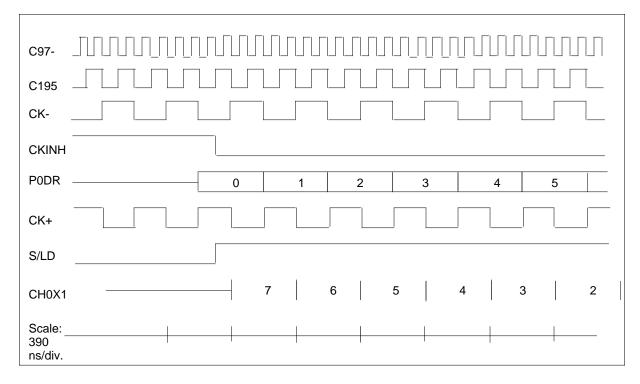

| C97–             |       |   |   |   |   |   |   |   |   |

|------------------|-------|---|---|---|---|---|---|---|---|

| C195             |       |   |   |   |   |   |   |   | T |

| CK–              |       |   |   |   |   |   |   |   | ] |

| CKINH            |       |   |   |   |   |   |   |   |   |

| P0DR             | <br>0 |   | 1 | 2 |   | 3 | 4 | 5 |   |

| CK+              |       |   |   |   |   |   |   |   |   |

| S/LD             |       |   |   |   |   |   |   |   |   |

| CH0X1            | <br>  | 7 |   | 6 | 5 | 4 | 3 |   | 2 |

| Scale:<br>390ns/ |       |   |   |   |   |   |   | _ |   |

## NT6X69MA

## **Product description**

The NT6X69MA card is almost identical to the NT6X69AB in structure. The wait-for-start-of-message (WAM) timeout value and the wait-for-acknowledge (WACK) timeout values for the NT6X69MA and the NT6X69AB are different. The WAM and WACK timeout values for the NT6X69AB are 1 ms. The WAM and WACK timeout values for the NT6X69MA are 50 ms. This change makes the card compatible with the enhanced network (ENET).

The NT6X69AB (CPP message protocol and tone card) incorporates the functionality of the NT6X79AA (CPCE tone generator card) into the NT6X69AA (CPP message protocol card).

### Location

The NT6X69MA is in slot 18 in a host XPM and slot 17 in an RCC.

# **Functional description**

## **Functional blocks**

The NT6X69MA consists of the following functional blocks:

- network message (NM) interface

- parallel speech bus (SB) message interface

- SB connection memory

- intermodule connection (IMC)

- tone generator and tone RAM

- protocol processor (PP)

- signaling processor (SP) and PP shared memory

- shelf reset generator

- cyclic redundancy check (CRC) ROM

- process timing ROM

- SP interface

### Network message interface

Data leaves and enters the shift registers of the NM interface in series. The channel 0 (CH0) signal from the active formatter prescribes the data movement. Before the CH0 time in each frame, data from the transmit hold register is loaded into the shift register. Before the CH0 time, data from the shift register is loaded into the receive holding register from the shift register.

The PP can read from or write into the holding registers at any time. The PP cannot perform this action during CH0.

#### Parallel speech bus message interface

The synchronous PP in the SB interface sends the message. The first half of the instruction cycle is dedicated to the PP to write to the transmit RAM or read from the receive RAM. In the second half of the instruction cycle, the system latches data to the transmit holding register from the transmit RAM. This event occurs according to the port/channel counter. The PP writes to the receive RAM from the receive holding register.

#### Speech bus connection memory

The connection memory arbitrates the access of the different service cards to the SB by each time slot. The SP accesses the connection memory with the same method as the PP/SP shared memory. The PP does not have access to the connection memory.

#### Intermodule connection interface

The IMC interface provides a 64 Kbit/s link to the mate unit. This link appears to the PP as an SB time slot. The FP assigns the particular time slot through the connection memory. The exchange of data occurs between the two shelves during the active CH0 time. The active clock gates the exchange. Errors can occur with the IMC link when the two shelves are not in synchronization.

#### Tone generator and tone PROM

Tone generation circuits on the NT6X69MA card consist of the R09 tone generation chip and the tone PROM.

#### Protocol processor

The PP accesses the following functional blocks:

- 8K×8 RAM shared with the SP

- CRC ROM for CRC calculation that the DMS-X protocol requires

- process timing ROM, which allows the firmware to synchronize to the frame

- RSTGEN, which allows the PP to initiate a shelf reset (MODRST) from the NT6X46 card (signaling processor memory plus card)

- INTGEN, which allows the PP to initiate a level-four interrupt to the SP

- NM interface

- speech bus interface

- IMC interface

## SP and PP shared memory

The SP and PP communicate through an 8K×8 block of RAM. The two processors share this block of RAM transparently. This block serves the following purposes:

- creates a work space for the PP

- provide a buffer for messages that the PP receives for the SP, and for messages that the SP queues for the PP

- provides an opcode area that allows the SP to apply the interfaces in an indirect method

### Shelf reset generator

The PP initiates a shelf reset with the use of the following sequence:

- 1. The PP clocks the reset flip–flop when the PP accesses the auxiliary reset strobe.

- 2. The output of the reset flip–flop transmits to the backplane and connected to the 6X46 card.

- 3. The NT6X46 card acknowledges the reset when the card loses activity. The NT6X46 card issues the module reset signal to the rest of the shelf.

- 4. The module reset that the NT6X46 card issues clears the reset flip–flop on the NT6X69 card.

### Cyclic redundancy check ROM

This ROM contains two tables. A two-stage CRC accumulation process uses these two tables. To access the upper page of the table, the PP must use the CRCL strobe followed by the CRCH strobe. To access the lower page, the PP must use the CRCL strobe.

### **Process timing ROM**

Process timing ROM allows the PP to synchronize each process time slot to the frame boundary. The port/channel counter addresses the programmable read only memory (PROM). The PP can read the PROM during any instruction cycle.

### Signaling processor interface

All address and control signals are buffered. An access sequence synchronizes SP requests and generates a read or write access cycle. This event occurs when a valid address falls in the range assigned to this card type. The interface is asynchronous and an acknowledge signal indicates the end of the access cycle.

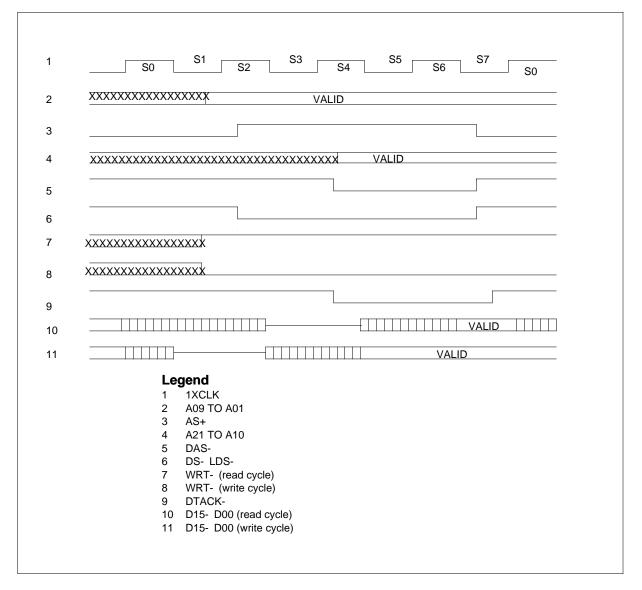

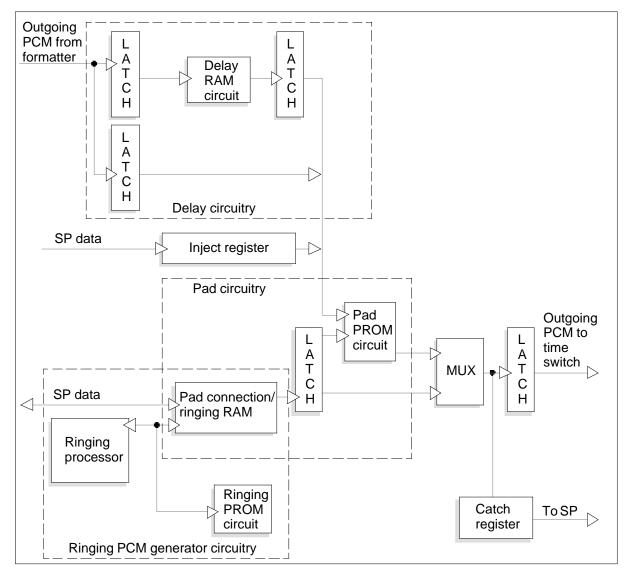

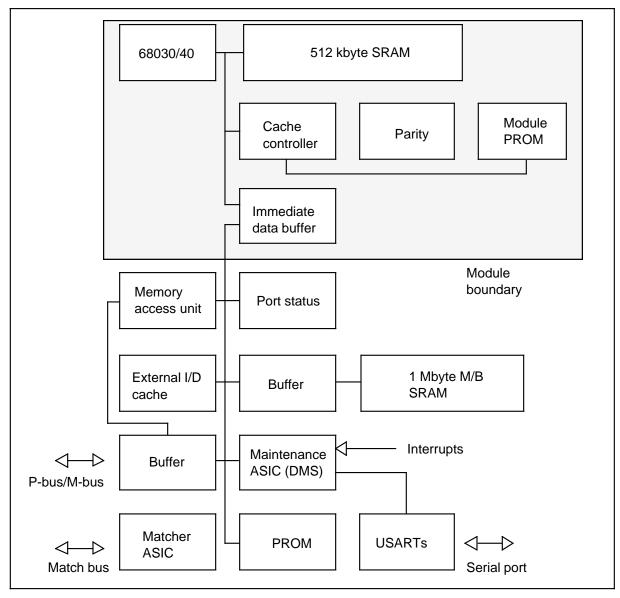

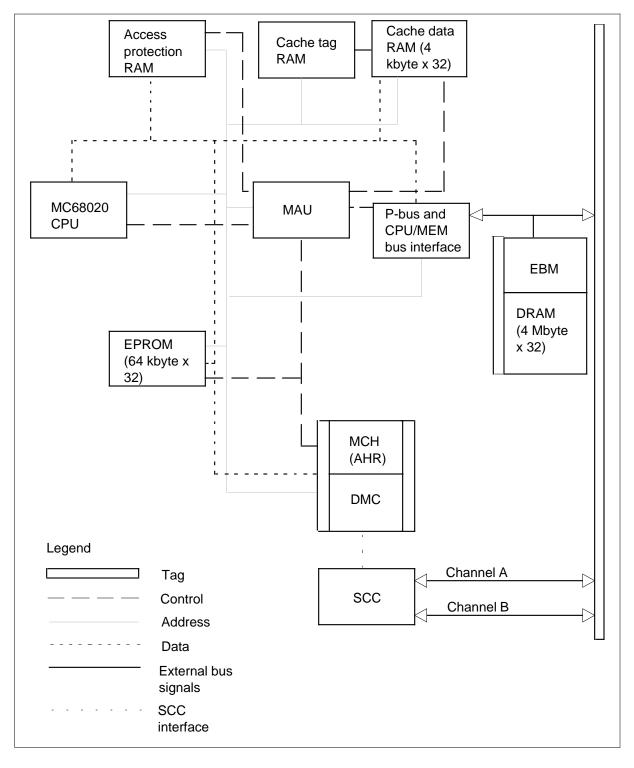

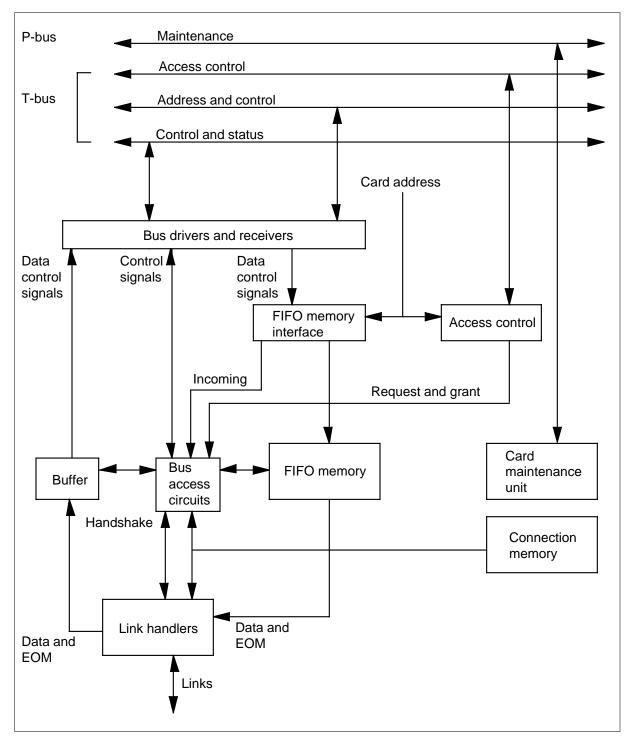

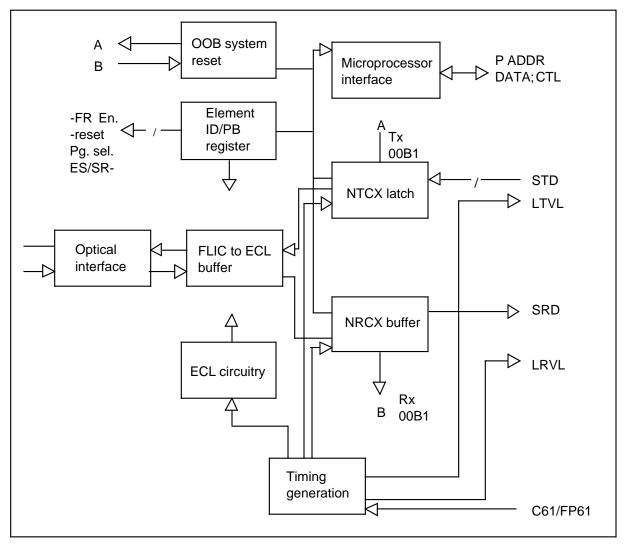

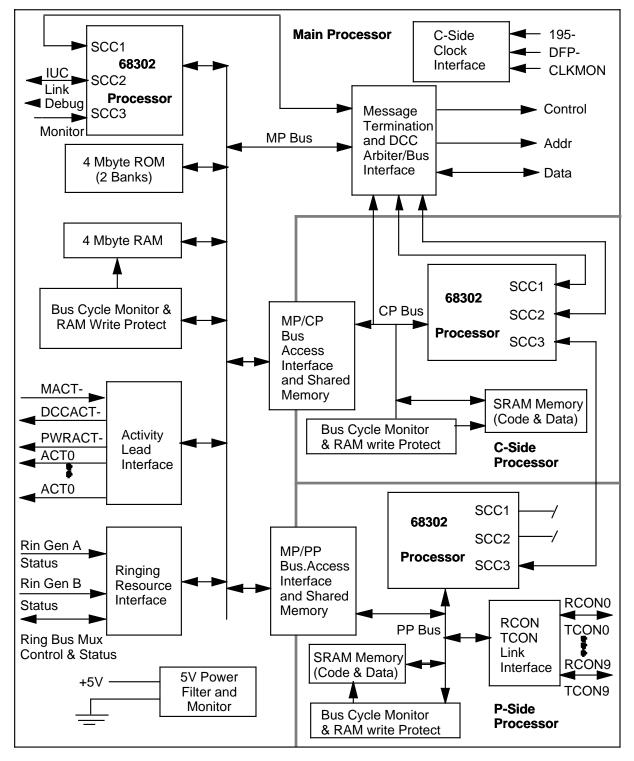

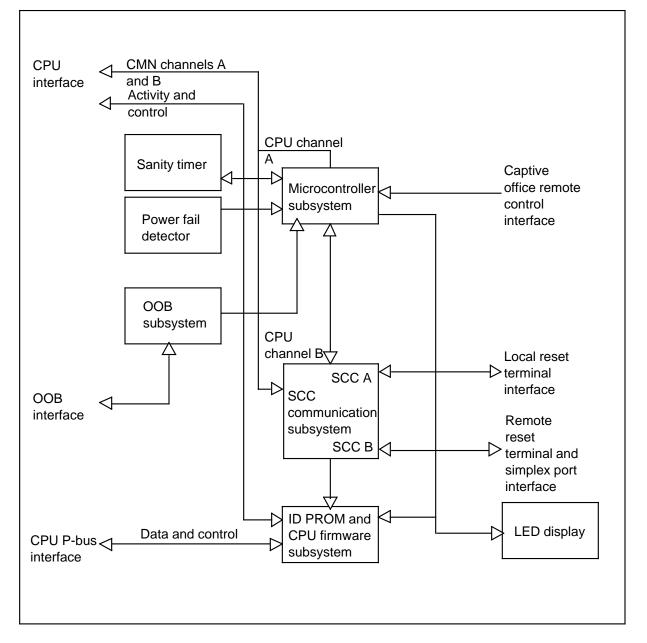

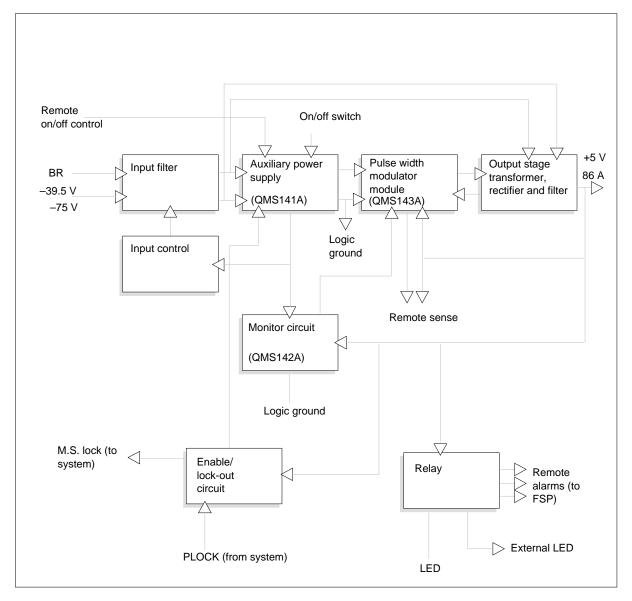

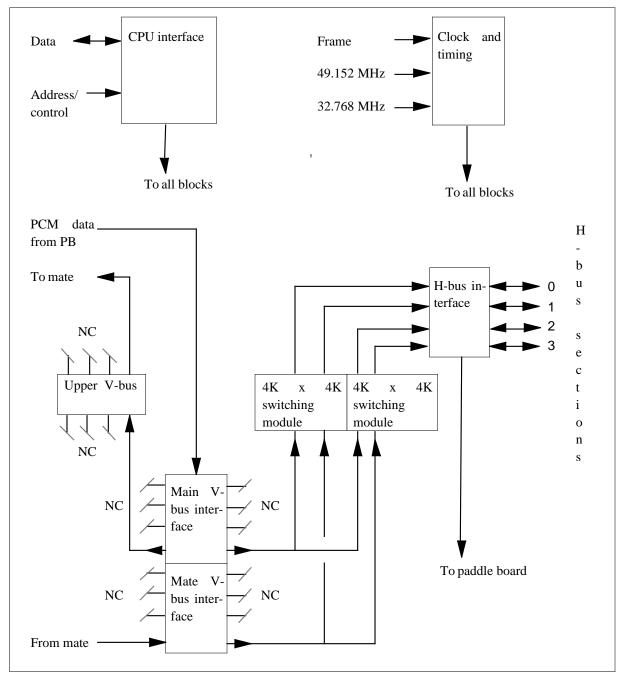

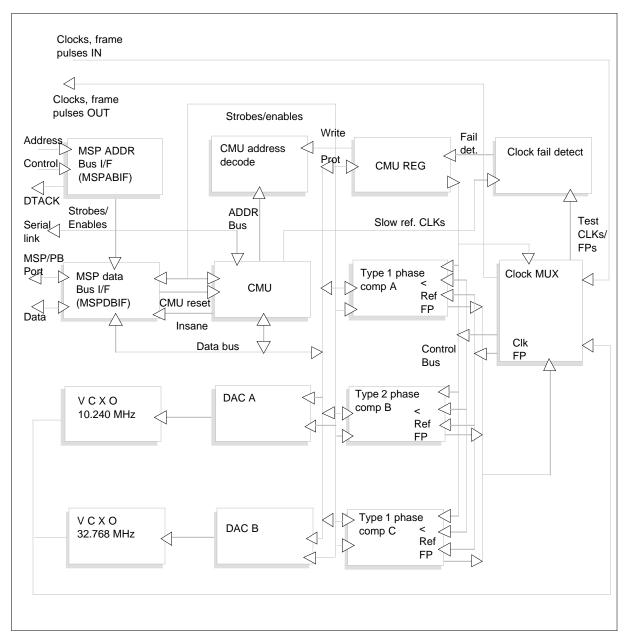

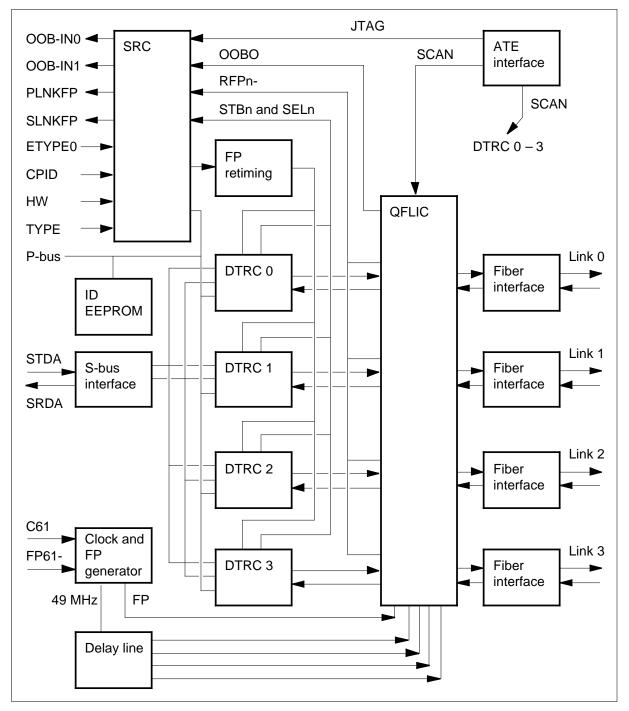

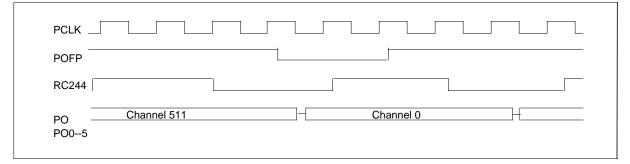

The relationship between the functional blocks appears in the following figure. A dashed line denotes the CM enable signal.

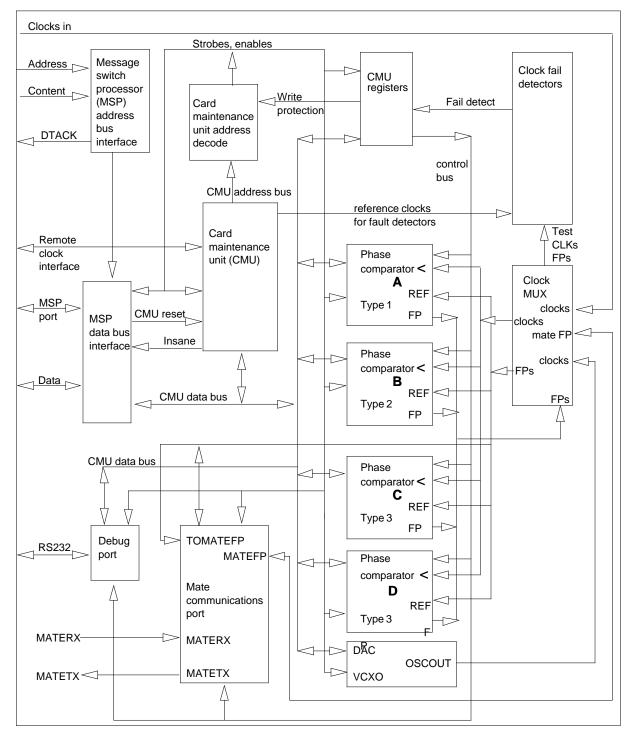

### NT6X69MA functional blocks

# Signaling

# Pin numbers

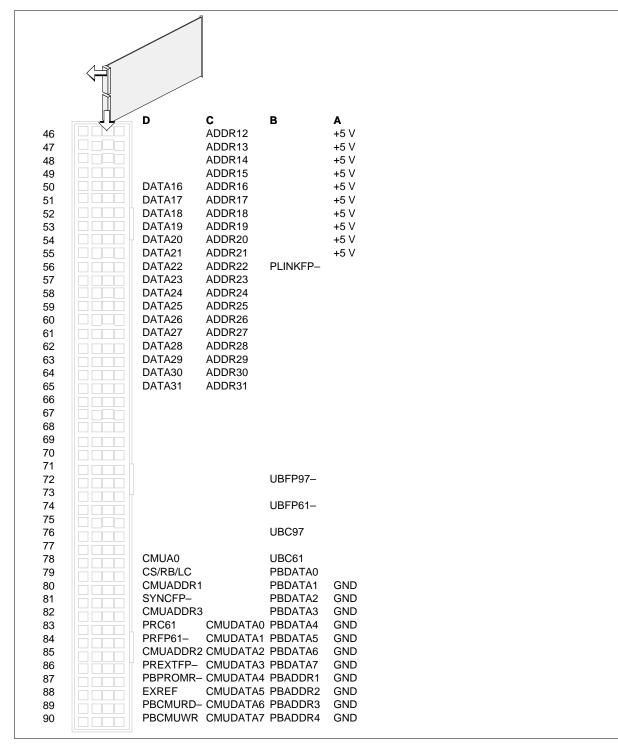

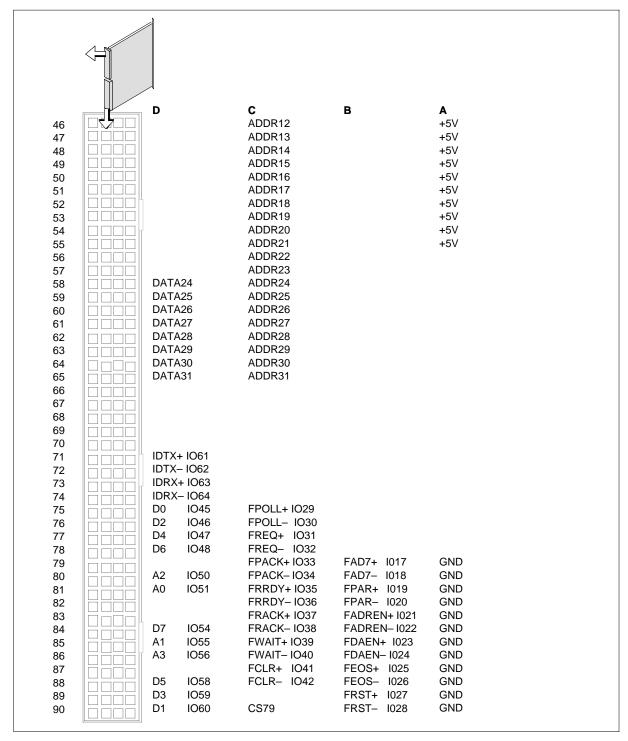

The pin numbers for NT6X69MA appear in the following figure.

*Note:* \* denotes test channel signals, backplane connection not needed. \*\* denotes additional signals on the 6902 card but not on the 6901. \*\*\* denotes temporary signals required by the NT6X79 card.

## NT6X69MA pin numbers

|         | <br>Α              | В         |          |    |                     |           |

|---------|--------------------|-----------|----------|----|---------------------|-----------|

| 1       | GND                | GND       |          |    |                     |           |

| 2       | 5V                 | 5V        |          |    |                     |           |

| 3       | 5V                 | 5V        | `        |    |                     |           |

| 4       | 5V                 | 5V        |          | ų. |                     |           |

| 5       | GND                | GND       |          | Ĭ  |                     |           |

| 6       | FP-                | C97T      |          |    |                     |           |

| 7       | GND                | GND       |          |    | Α                   | В         |

| 8       | -ACT               | CILD      | 41       |    | GND                 | GND       |

| 9       | C195TB*            |           | 42       |    | ADDR12+             |           |

| 5<br>10 | CPROCS-*           |           | 43       |    | ADDR13+             | D0*       |

|         | GND                | GND       | 44       |    | ADDR14+             | D1*       |

| 11      |                    | GND       | 45       |    | ADDR15+             | D2*       |

| 12      | DAS-               | 007 D     | 46       |    | ADDR16+             | D3*       |

| 13      | LDS-               | С97-В     | 47       |    | ADDR17+             | D4*       |

| 14      | DTACK-             | CPROCB    | 48       |    | ADDR17+             | D5*       |

| 15      | UDS-               | RUN*      | 40<br>49 |    | ADDR10+             | D6*       |

| 16      | WRT-               | TCEN-*    | 49<br>50 |    | ADDR 19+<br>ADDR20+ | D7*       |

| 17      | IMCOUT**           |           | 50<br>51 |    | ADDR20+<br>ADDR21+  | וט        |

| 18      | GND                | INT4REQ** | 51<br>52 |    |                     | DESTXT0-  |

| 19      |                    |           |          |    | SEN0                |           |

| 20      |                    |           | 53       |    | SEN1                | DESTXT1-  |

| 21      | PIN0               | POUT0     | 54       |    | SEN2                | 00.01/70  |

| 22      | PIN1               | POUT1     | 55       |    | PSPEN+              | SRCXT0-   |

| 23      | PIN2               | POUT2     | 56       |    | CSPEN+              | SRCXT1-   |

| 24      | PIN3               | POUT3     | 57       |    | GND                 | GND       |

| 25      | PIN4               | POUT4     | 58       |    | DATA00+             | SRC0*     |

| 26      | PIN5               | POUT5     | 59       |    | DATA01+             | SRC1*     |

| 27      | PIN6               | POUT6     | 60       |    | DATA02+             | SRC2*     |

| 28      | PIN7               | POUT7     | 61       |    | DATA03+             | SRC3*     |

| 29      | ADDR01+            |           | 62       |    | DATA04+             | SRC4*     |

| 30      | ADDR02+            |           | 63       |    | DATA05+             | SRC5*     |

| 31      | ADDR03+            |           | 64       |    | GND                 | SRC6*     |

| 32      | ADDR04+            |           | 65       |    | DATA06+             | SRC7*     |

| 33      | ADDR05+            |           | 66       |    | DATA07+             |           |

| 34      | GND                | GND       | 67       |    |                     | CH0S0     |

| 34      | ADDR06+            | -FPM      | 68       |    |                     | CH0R0     |

| 36      | ADDR07+            | GND       | 69       |    |                     | CH0S1     |

| 30      | ADDR07+            | C97M+     | 70       |    |                     | CHOR1     |

|         | ADDR08+<br>ADDR09+ | GND       | 71       |    |                     | (T1***)   |

| 38      |                    |           | 72       |    |                     | (T2***)   |

| 39      | ADDR10+            | CHOT      | 73       |    |                     | (T2**)    |

| 40      | ADDR11+            | CH0M      | 74       |    |                     | AUXRST-** |

|         |                    |           | 75       |    |                     | MODRST-** |

|         |                    |           | 76       |    | GND                 | GND       |

|         |                    |           | 77       |    |                     |           |

|         |                    |           | 78       |    | GND                 | GND       |

|         |                    |           | 78<br>79 |    | GND                 | UND       |

|         |                    |           | 79<br>80 |    | GND                 | GND       |

|         |                    |           | 00       |    | GND                 | GND       |

|         |                    |           |          |    |                     |           |

|         | <br>               |           |          |    |                     |           |

|         | <br>               |           |          |    |                     |           |

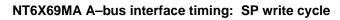

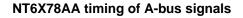

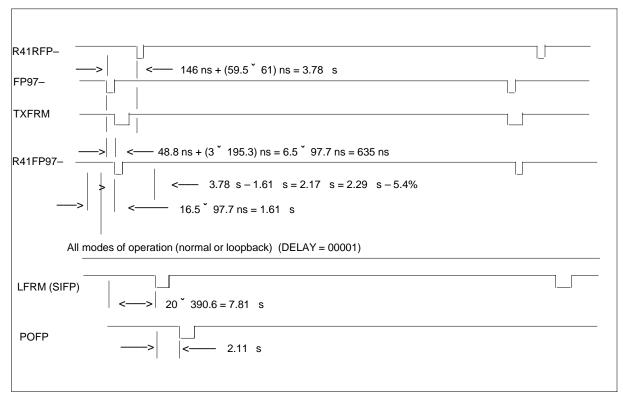

## Timing

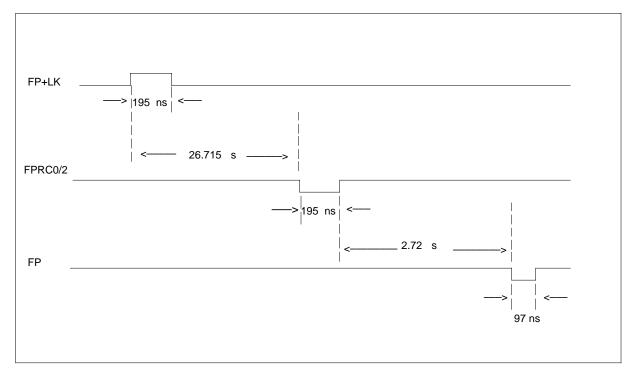

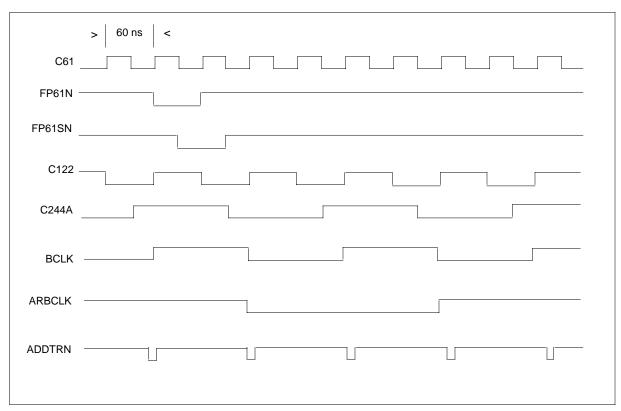

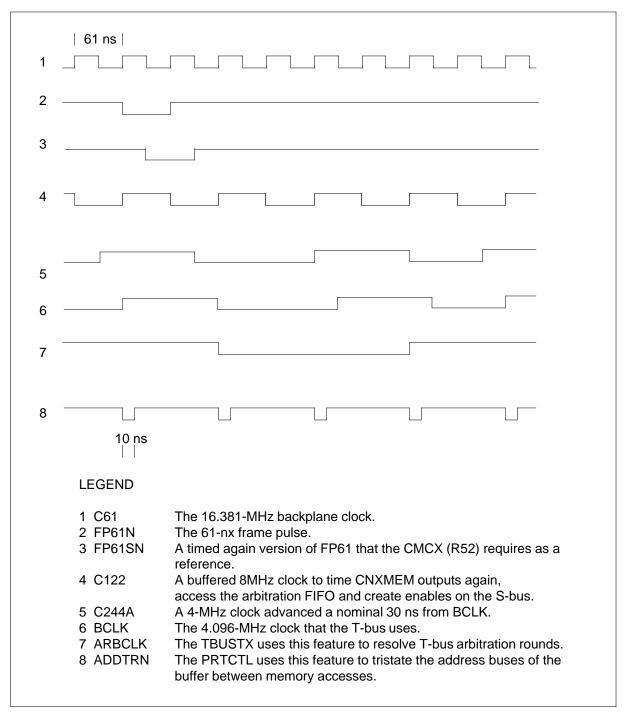

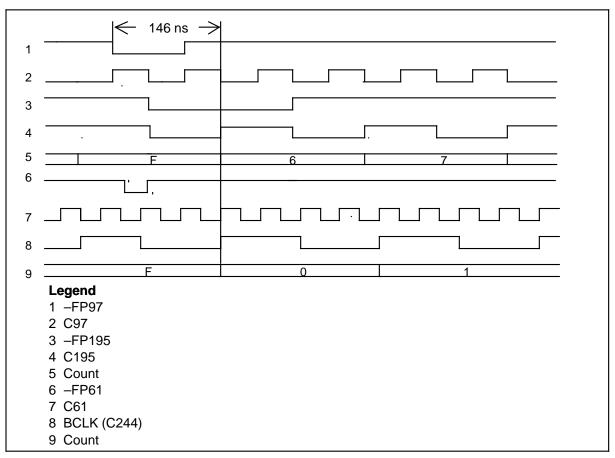

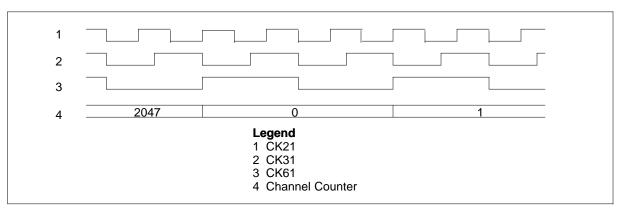

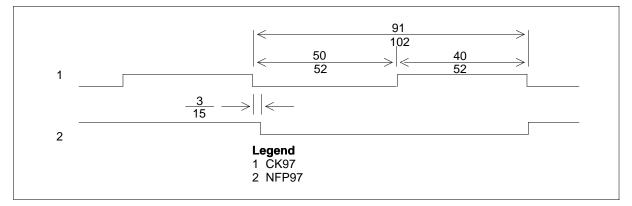

The timing for the NT6X69MA appears in the following figures.

| с97-          |   |

|---------------|---|

| C195F         |   |

| PROCYC+       |   |

| DS (U98P11)   |   |

| DAS-          | _ |

| ADRM (U115P9) | 1 |

| DTACK-        |   |

| WRT-          |   |

| Scale:<br>195 |   |

#### NT6X69MA A-bus interface timing: SP read cycle

| C195F         |  |

|---------------|--|

| PROCYC+       |  |

| WRT-          |  |

| ENMBOUT-      |  |

| ENCMOUT-      |  |

| DTACK-        |  |

| Scale:<br>195 |  |

# NT6X69MA (end)

## NT6X69MA network module interface timing

# NT6X69QA

## **Product description**

The NT6X69QA card is almost identical to the NT6X69AB in structure. The wait-for-start-of-message (WAM) timeout value and the wait-for-acknowledge (WACK) timeout values for the NT6X69QA and the NT6X69AB are different. The WAM and WACK timeout values for the NT6X69AB are 1 ms. The WAM and WACK timeout values for the NT6X69QA are 50 ms. This change makes the card compatible with the enhanced network (ENET).

The NT6X69AB (CPP message protocol and tone card) incorporates the functionality of the NT6X79AA (CPCE tone generator card) into the NT6X69AA (CPP message protocol card).

### Location

The NT6X69QA is in slot 18 in a host XPM and slot 17 in an RCC.

# **Functional description**

### **Functional blocks**

The NT6X69QA consists of the following functional blocks:

- network message (NM) interface

- parallel speech bus (SB) message interface

- SB connection memory

- intermodule connection (IMC)

- tone generator and tone RAM

- protocol processor (PP)

- signaling processor (SP) and PP shared memory

- shelf reset generator

- cyclic redundancy check (CRC) ROM

- process timing ROM

- SP interface

### Network message interface

Data leaves and enters the shift registers of the NM interface in series. The channel 0 (CH0) signal from the active formatter prescribes the data movement. Before the CH0 time in each frame, data from the transmit hold register is loaded into the shift register. Before the CH0 time, data from the shift register is loaded into the receive holding register from the shift register.

The PP can read from or write into the holding registers at any time. The PP cannot perform this action during CH0.

#### Parallel speech bus message interface

The synchronous PP in the SB interface sends the message. The first half of the instruction cycle is dedicated to the PP to write to the transmit RAM or read from the receive RAM. In the second half of the instruction cycle, the system latches data to the transmit holding register from the transmit RAM. This event occurs according to the port/channel counter. The PP writes to the receive RAM from the receive holding register.

#### Speech bus connection memory

The connection memory arbitrates the access of the different service cards to the SB by each time slot. The SP accesses the connection memory with the same method as the PP/SP shared memory. The PP does not have access to the connection memory.

#### Intermodule connection interface

The IMC interface provides a 64 Kbit/s link to the mate unit. This link appears to the PP as an SB time slot. The FP assigns the particular time slot through the connection memory. The exchange of data occurs between the two shelves during the active CH0 time. The active clock gates the exchange. Errors can occur with the IMC link when the two shelves are not in synchronization.

#### Tone generator and tone PROM

Tone generation circuits on the NT6X69QA card consist of the R09 tone generation chip and the tone PROM.

#### Protocol processor

The PP accesses the following functional blocks:

- 8K×8 RAM shared with the SP

- CRC ROM for CRC calculation that the DMS-X protocol requires

- process timing ROM, which allows the firmware to synchronize to the frame

- RSTGEN, which allows the PP to initiate a shelf reset (MODRST) from the NT6X46 card (signaling processor memory plus card)

- INTGEN, which allows the PP to initiate a level-four interrupt to the SP

- NM interface

- speech bus interface

- IMC interface

### SP and PP shared memory

The SP and PP communicate through an 8K×8 block of RAM. The two processors share this block of RAM transparently. This block serves the following purposes:

- creates a work space for the PP

- provide a buffer for messages that the PP receives for the SP, and for messages that the SP queues for the PP

- provides an opcode area that allows the SP to apply the interfaces in an indirect method

### Shelf reset generator

The PP initiates a shelf reset with the use of the following sequence:

- 1. The PP clocks the reset flip–flop when the PP accesses the auxiliary reset strobe.

- 2. The output of the reset flip–flop transmits to the backplane and connected to the 6X46 card.

- 3. The NT6X46 card acknowledges the reset when the card loses activity. The NT6X46 card issues the module reset signal to the rest of the shelf.

- 4. The module reset that the NT6X46 card issues clears the reset flip–flop on the NT6X69 card.

### Cyclic redundancy check ROM

This ROM contains two tables. A two-stage CRC accumulation process uses these two tables. To access the upper page of the table, the PP must use the CRCL strobe followed by the CRCH strobe. To access the lower page, the PP must use the CRCL strobe.

### **Process timing ROM**

Process timing ROM allows the PP to synchronize each process time slot to the frame boundary. The port/channel counter addresses the programmable read only memory (PROM). The PP can read the PROM during any instruction cycle.

### Signaling processor interface

All address and control signals are buffered. An access sequence synchronizes SP requests and generates a read or write access cycle. This event occurs when a valid address falls in the range assigned to this card type. The interface is asynchronous and an acknowledge signal indicates the end of the access cycle.

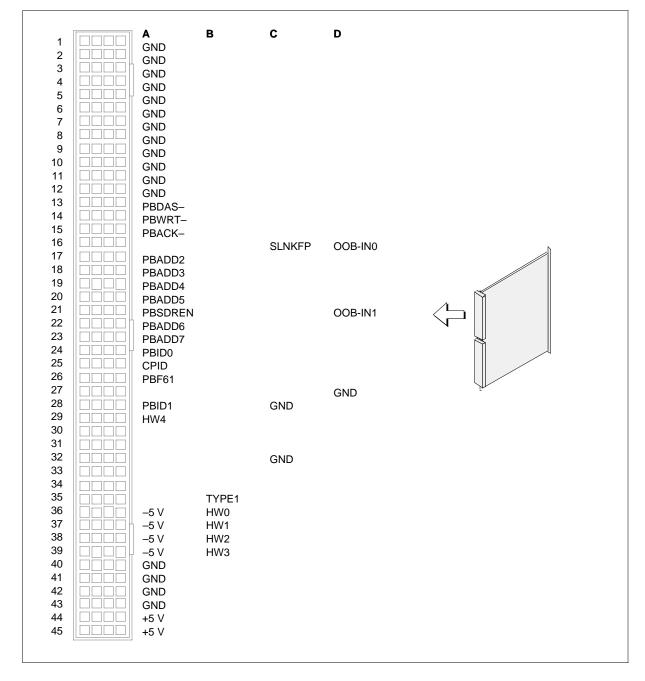

# Signaling

# Pin numbers

The pin numbers for NT6X69QA appear in the following figure.

*Note:* \* denotes signals defined in previous versions of the NT6X69, but are no longer required. \*\* denotes signals defined in NT6X69AA versions that were configured with NT6X79 circuit packs. \*\*\* denotes signals that are not used on the NT6X69QA, but are defined on the backplane at the slot occupied by the NT6X69QA in either an XPM or an RSCS (CPM).

# NT6X69QA (end)

## NT6X69QA pin numbers

|    | Α              | В                 |          |   |              |          |

|----|----------------|-------------------|----------|---|--------------|----------|

| 1  | GND            | GND               |          |   |              |          |

| 2  | 5V             | 5V                |          |   |              |          |

| 3  | 5V             | 5V                | ·        |   |              |          |

| 4  | 5V             | 5V                |          |   |              |          |

| 5  | GND            | GND               |          |   |              |          |

| 6  | FP-            | C97T              |          |   |              |          |

| 7  | GND            | GND               |          |   | Α            | В        |

| 8  | -ACT           | OND               | 41       |   | GND          | GND      |

| 9  | C195TB*        | FP40–/i***        | 42       |   | ADDR12       |          |

| 10 | CPROCS-*       | 1140 //           | 43       |   | ADDR13       | DEST00   |

|    | GND            | GND               | 44       |   | ADDR14       | DEST01   |

| 12 | DAS-           | PERINT3-***       | 45       |   | ADDR15       | DEST02   |

|    | LDS-           | C97–B*            | 46       |   | ADDR16       | DEST03   |

| 13 | LDS-<br>DTACK- | C97–B*<br>CPROCB* | 47       |   | ADDR17       | DEST04   |

|    |                |                   | 48       |   | ADDR18       | DEST05   |

| 15 | UDS-           | RUN*              | 49       |   | ADDR19       | DEST06   |

| 16 | RDWRT-         | TADDR             | 50       |   | ADDR19       | DEST07   |

| 17 | IMCTX          | IMCRX             | 51       |   | ADDR20       | BLOID    |

| 18 | GND            | INT4REQ-          | 52       |   | SEN0         | DESTXT0  |

| 19 | PINA***        | POUTA***          | 53       |   | SEN0         | DESTXT1  |

| 20 | PINB***        | POUTB***          | 54       |   | SEN1<br>SEN2 | DESTATI  |

| 21 | PIN0           | POUT0             | 55       |   | PSPEN+       | CDCVTO * |

| 22 | PIN1           | POUT1             | 55<br>56 |   |              | SRCXT0-* |

| 23 | PIN2           | POUT2             |          |   | CSPEN+       | SRCXT1-* |

| 24 | PIN3           | POUT3             | 57       |   | GND          | GND      |

| 25 | PIN4           | POUT4             | 58       |   | DATA00       | SRC0*    |

| 26 | PIN5           | POUT5             | 59       |   | DATA01       | SRC1*    |

| 27 | PIN6           | POUT6             | 60       |   | DATA02       | SRC2*    |

| 28 | PIN7           | POUT7             | 61       |   | DATA03       | SRC3*    |

| 29 | ADDR01         | CMSGOUT0***       | 62       |   | DATA04       | SRC4*    |

| 30 | ADDR02         | CMSGIN0***        | 63       |   | DATA05       | SRC5*    |

| 31 | ADDR03         | CMSGOUT2***       | 64       |   | GND          | SRC6*    |

| 32 | ADDR04         | CMSGIN2***        | 65       |   | DATA06       | SRC7*    |

| 33 | ADDR05         | -HOST/REM***      | 66       |   | DATA07       |          |

| 34 | GND            | GND               | 67       |   | DATA08       | CH0S0    |

| 35 | ADDR06         | -FPM              | 68       |   | DATA09       | CH0R0    |

| 36 | ADDR07         | GND               | 69       |   | DATA10       | CH0S1    |

| 37 | ADDR08         | C97M+             | 70       |   | DATA11       | CH0R1    |

| 38 | ADDR09         | GND               | 71       |   | DATA12       | T1**     |

| 39 | ADDR10         | CHOTIN            | 72       |   | DATA13       | T2**     |

| 40 | ADDR11         | CHOMIN            | 73       |   | DATA14       | T3**     |

|    |                |                   | 74       |   | DATA15       | MODRST-  |

|    |                |                   | 75       |   |              | AUXRST-  |

|    |                |                   | 76       |   | GND          | GND      |

|    |                |                   | 77       |   | +12***       | +12***   |

|    |                |                   | 78       |   | GND          | GND      |

|    |                |                   | 79       |   | -12***       | -12***   |

|    |                |                   | 80       |   | GND          | GND      |

|    |                |                   |          | L |              |          |

# NT6X70AA

## **Product description**

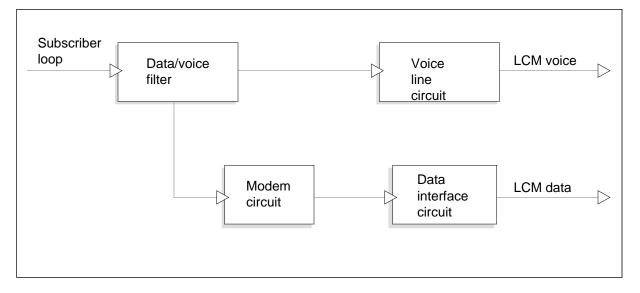

The NT6X70AA continuity tone detector (CTD) card verifies the continuity of the voice/data path between digital trunk controllers (DTC). To verify the continuity, the NT6X70AA detects tones in the common channel interoffice signaling (CCIS) call process.

### Location

The NT6X70AA occupies one position in a DTC.

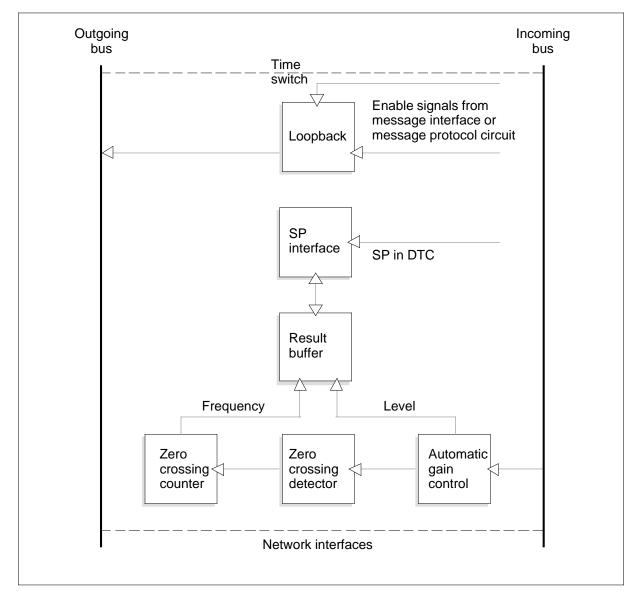

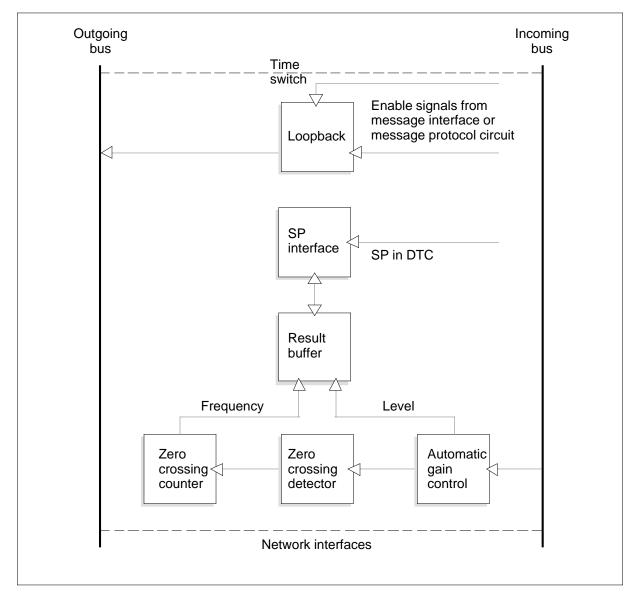

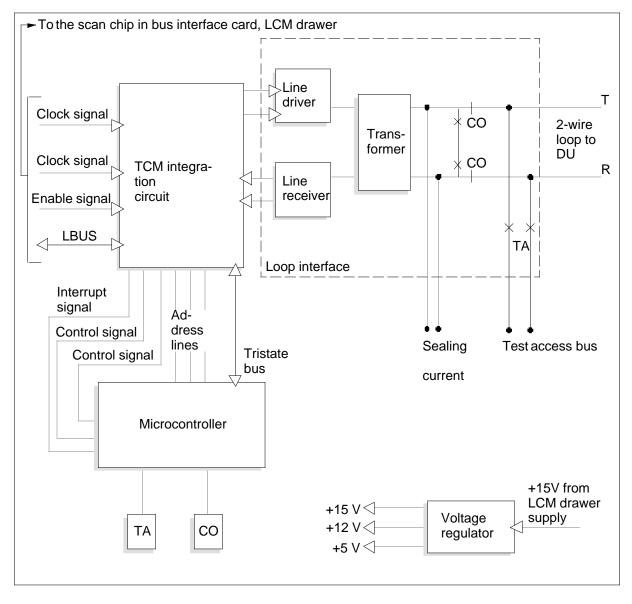

# **Functional description**